Nivel: Básico — Implementar un sistema donde un motor solo funciona cuando se presionan dos botones simultáneamente.

Objetivo y caso de uso

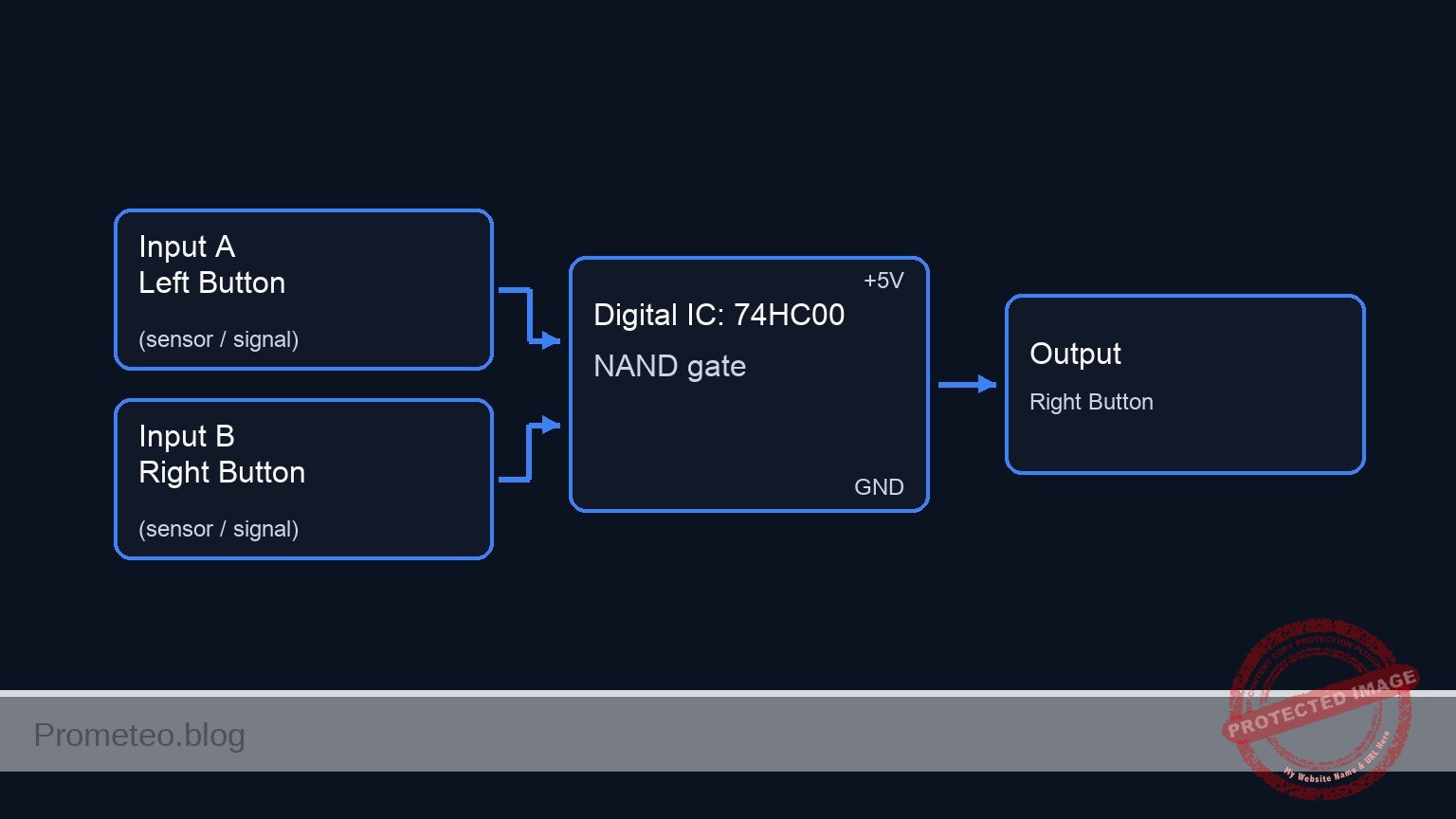

En esta sesión, construirás un circuito lógico de seguridad utilizando un 74HC00 (cuádruple puerta NAND de 2 entradas) para controlar un motor de CC. El motor solo se activará cuando se accionen dos pulsadores separados al mismo tiempo, imitando un dispositivo de seguridad de «mando a dos manos».

Por qué es útil:

* Seguridad industrial: Evita que los operarios introduzcan las manos en una prensa hidráulica o máquina de corte mientras está en movimiento.

* Prevención de accidentes: Asegura que ambas manos estén ocupadas en los controles durante la fase peligrosa de la operación.

* Composición lógica: Demuestra cómo crear una función AND utilizando puertas NAND universales.

Resultado esperado:

* Estado de reposo: La salida lógica es LOW (0 V); el motor está APAGADO.

* Pulsación única: La salida lógica permanece en LOW (0 V); el motor permanece APAGADO.

* Pulsación dual: La salida lógica pasa a HIGH (5 V); el relé se activa; el motor funciona.

* Manejo de corriente: La puerta lógica excita un transistor, que conmuta de forma segura la bobina del relé de alta corriente.

Público objetivo y nivel:

Estudiantes de electrónica básica y aficionados interesados en aplicaciones de lógica digital.

Materiales

- V1: Fuente de tensión de 5 V CC, función: Alimentación de la lógica y la bobina del relé.

- V2: Fuente de tensión de 12 V CC, función: Alimentación del motor.

- U1: 74HC00, función: CI de cuádruple puerta NAND de 2 entradas.

- S1: Pulsador (normalmente abierto), función: Interruptor de seguridad de mano izquierda.

- S2: Pulsador (normalmente abierto), función: Interruptor de seguridad de mano derecha.

- R1: Resistencia de 10 kΩ, función: Pull-down para S1.

- R2: Resistencia de 10 kΩ, función: Pull-down para S2.

- R3: Resistencia de 1 kΩ, función: Limitación de corriente de base para Q1.

- Q1: Transistor NPN 2N2222, función: Controlador del relé.

- D1: Diodo 1N4007, función: Protección flyback para la bobina del relé.

- K1: Relé SPDT de 5 V, función: Interfaz de conmutación de alta potencia.

- M1: Motor de 12 V CC, función: Actuador (carga).

Pin-out del CI utilizado (74HC00)

Chip: 74HC00 (Cuádruple puerta NAND de 2 entradas)

| Pin | Nombre | Función lógica | Conexión en este caso |

|---|---|---|---|

| 1 | 1 A | Entrada A (Puerta 1) | Conectado a S1 (Nodo BTN_L) |

| 2 | 1B | Entrada B (Puerta 1) | Conectado a S2 (Nodo BTN_R) |

| 3 | 1Y | Salida (Puerta 1) | Conectado a entradas de la Puerta 2 (Nodo NAND_INTER) |

| 4 | 2 A | Entrada A (Puerta 2) | Conectado al Nodo NAND_INTER |

| 5 | 2B | Entrada B (Puerta 2) | Conectado al Nodo NAND_INTER |

| 6 | 2Y | Salida (Puerta 2) | Conectado a R3 (Nodo LOGIC_OUT) |

| 7 | GND | Tierra (Masa) | Conectado al Nodo 0 |

| 14 | VCC | Alimentación | Conectado al Nodo VCC |

Nota: Los pines del 8 al 13 no se utilizan y deberían conectarse idealmente a GND o VCC en una instalación permanente para evitar ruido, aunque se dejan flotantes para este ejercicio básico en protoboard.

Guía de conexionado

Construye el circuito siguiendo estas conexiones de nodos. Asegúrate de que la fuente de alimentación esté apagada mientras construyes.

Alimentación y entradas:

* V1 (+): Se conecta al nodo VCC.

* V1 (-) / V2 (-): Se conecta al nodo 0 (Tierra común).

* S1: Se conecta entre VCC y el nodo BTN_L.

* R1: Se conecta entre el nodo BTN_L y 0.

* S2: Se conecta entre VCC y el nodo BTN_R.

* R2: Se conecta entre el nodo BTN_R y 0.

Procesamiento lógico (Usando U1 como puerta AND):

* U1 (Pin 14): Se conecta a VCC.

* U1 (Pin 7): Se conecta a 0.

* U1 (Pin 1): Se conecta al nodo BTN_L.

* U1 (Pin 2): Se conecta al nodo BTN_R.

* U1 (Pin 3): Se conecta al nodo NAND_INTER (Salida de la primera etapa).

* U1 (Pin 4 y Pin 5): Ambos se conectan al nodo NAND_INTER (Configura la Puerta 2 como inversor).

* U1 (Pin 6): Se conecta al nodo LOGIC_OUT.

Etapa de salida:

* R3: Se conecta entre el nodo LOGIC_OUT y el nodo BASE.

* Q1 (Base): Se conecta al nodo BASE.

* Q1 (Emisor): Se conecta al nodo 0.

* Q1 (Colector): Se conecta al nodo RELAY_COIL_LO.

* K1 (Bobina +): Se conecta a VCC.

* K1 (Bobina -): Se conecta al nodo RELAY_COIL_LO.

* D1 (Ánodo): Se conecta al nodo RELAY_COIL_LO.

* D1 (Cátodo): Se conecta a VCC (Paralelo a la bobina, polarización inversa).

Circuito del motor:

* V2 (+): Se conecta al contacto Común de K1 (COM).

* K1 (NO – Normalmente Abierto): Se conecta al nodo MOTOR_POS.

* M1 (+): Se conecta al nodo MOTOR_POS.

* M1 (-): Se conecta al nodo 0.

Diagrama de bloques conceptual

Esquemático

+-----------------------------------------------------------------------------+

| DUAL SAFETY MOTOR ACTIVATION BLOCK DIAGRAM |

+-----------------------------------------------------------------------------+

1. INPUTS & LOGIC STAGE (5 V Domain)

(Both buttons must be pressed to activate the output)

V1(5 V)

|

+---> [ S1: Left Button ] ---+--(BTN_L)------\

| \

v \

[ R1: 10k ] +---> [ U1:A (NAND) ] --(NAND_INTER)--> [ U1:B (NOT*) ] --(LOGIC_OUT)-->

| / (Pins 1 & 2) (Pins 4 & 5) |

GND / *Wired as Inverter |

/ |

V1(5 V) / |

| / |

+---> [ S2: Right Button ] --+--(BTN_R)---/ |

| |

v |

[ R2: 10k ] |

| |

GND |

|

+-------------------------------------------------------------------------------------------------------------------+

| |

| 2. RELAY DRIVER STAGE (5 V Domain) |

| (Low-Side Transistor Switch) |

| |

| (From Logic Above) |

| | V1(5 V) |

| v | |

| [ R3: 1k ] | |

| | v |

| +----------------------------------> [ Q1: Base ] |

| : |

| (Controls Current Flow) |

| : |

| +-----------------+ |

| | |

| [ Q1: Collector ] |

| ^ |

| | |

| (Node: RELAY_COIL_LO) |

| | |

| +-----------------+-----------------+ |

| | | |

| [ K1: Relay Coil ] [ D1: Diode ] |

| (Control Side) (Protection) |

| | (Anode to Coll) |

| | (Cathode to VCC) |

| +-----------------+-----------------+ |

| ^ |

| | |

| V1(5 V) |

| |

| [ Q1: Emitter ] |

| | |

| v |

| GND |

| |

+-------------------------------------------------------------------------------------------------------------------+

| |

| 3. MOTOR OUTPUT STAGE (12 V Domain) |

| (High Power Load) |

| |

| (Magnetic Link from K1 Coil Above) |

| | |

| v |

| V2(12 V) ---------> [ K1: Switch (COM to NO) ] --(MOTOR_POS)--> [ M1: 12 V Motor ] ----> GND |

| |

+-------------------------------------------------------------------------------------------------------------------+

Tabla de verdad

Estamos utilizando dos puertas NAND. La primera combina las entradas; la segunda invierte el resultado para crear una función AND.

| S1 (Izquierda) | S2 (Derecha) | U1 Pin 3 (1Y) | U1 Pin 6 (2Y) | Estado del motor |

|---|---|---|---|---|

| 0 (OFF) | 0 (OFF) | 1 (Alto) | 0 (Bajo) | PARADO |

| 0 (OFF) | 1 (ON) | 1 (Alto) | 0 (Bajo) | PARADO |

| 1 (ON) | 0 (OFF) | 1 (Alto) | 0 (Bajo) | PARADO |

| 1 (ON) | 1 (ON) | 0 (Bajo) | 1 (Alto) | EN MARCHA |

Mediciones y pruebas

- Comprobación en reposo: Enciende V1. No presiones ningún botón. Mide el voltaje en

LOGIC_OUT(Pin 6). Debería ser ~0 V. El motor debería estar parado. - Validación de entradas: Presiona solo S1. Mide el voltaje en el Pin 1. Debería ser 5 V. El Pin 2 debería ser 0 V. La salida en el Pin 6 debe permanecer en 0 V.

- Prueba activa: Presiona y mantén presionados ambos botones S1 y S2 simultáneamente.

- Escucha el «clic» del relé K1.

- Observa a M1 girando.

- Mide el voltaje en

LOGIC_OUT; debería estar cerca de 5 V.

- Prueba de liberación: Suelta solo un botón. El motor debe detenerse inmediatamente.

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Practical case: Logic AND gate controlling a relay and motor

* ==============================================================================

* COMPONENT MODELS

* ==============================================================================

* Generic NPN Transistor Model (2N2222)

.model 2N2222MOD NPN(Is=14.34f Xti=3 Eg=1.11 Vaf=74.03 Bf=255.9 Ne=1.307 Ise=14.34f Ikf=.2847 Xtb=1.5 Br=6.092 Nc=2 Isc=0 Ikr=0 Rc=1 Cjc=7.306p Mjc=.3416 Vjc=.75 Fc=.5 Cje=22.01p Mje=.377 Vje=.75 Tr=46.91n Tf=411.1p Itf=.6 Vtf=1.7 Xtf=3 Rb=10)

* Generic Diode Model (1N4007)

.model D1N4007 D(IS=7.02767n RS=0.0341512 N=1.80803 EG=1.11 XTI=3 BV=1000 IBV=10m CJO=10p VJ=0.7 M=0.5 FC=0.5 TT=100n)

* Ideal Switch Model for Buttons and Relay Contact

* Vt=2.5V (Logic Threshold), Ron=0.1 Ohm, Roff=10 MegOhm

.model SW_IDEAL SW(Vt=2.5 Vh=0.1 Ron=0.1 Roff=10Meg)

* ==============================================================================

* POWER SUPPLIES

* ==============================================================================

* V1: 5V DC Supply for Logic and Relay Coil

V1 VCC 0 DC 5

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Practical case: Logic AND gate controlling a relay and motor

* ==============================================================================

* COMPONENT MODELS

* ==============================================================================

* Generic NPN Transistor Model (2N2222)

.model 2N2222MOD NPN(Is=14.34f Xti=3 Eg=1.11 Vaf=74.03 Bf=255.9 Ne=1.307 Ise=14.34f Ikf=.2847 Xtb=1.5 Br=6.092 Nc=2 Isc=0 Ikr=0 Rc=1 Cjc=7.306p Mjc=.3416 Vjc=.75 Fc=.5 Cje=22.01p Mje=.377 Vje=.75 Tr=46.91n Tf=411.1p Itf=.6 Vtf=1.7 Xtf=3 Rb=10)

* Generic Diode Model (1N4007)

.model D1N4007 D(IS=7.02767n RS=0.0341512 N=1.80803 EG=1.11 XTI=3 BV=1000 IBV=10m CJO=10p VJ=0.7 M=0.5 FC=0.5 TT=100n)

* Ideal Switch Model for Buttons and Relay Contact

* Vt=2.5V (Logic Threshold), Ron=0.1 Ohm, Roff=10 MegOhm

.model SW_IDEAL SW(Vt=2.5 Vh=0.1 Ron=0.1 Roff=10Meg)

* ==============================================================================

* POWER SUPPLIES

* ==============================================================================

* V1: 5V DC Supply for Logic and Relay Coil

V1 VCC 0 DC 5

* V2: 12V DC Supply for Motor

V2 V_MOTOR_RAIL 0 DC 12

* ==============================================================================

* INPUT STAGE (Safety Switches)

* ==============================================================================

* Simulation of User Pressing Buttons:

* We use Pulse sources (V_ACT_...) to control ideal switches (S1, S2).

* This preserves the Pull-down resistor topology.

* S1: Left Safety Switch (Pushbutton NO)

* Connects VCC to BTN_L when pressed.

* Pulse Pattern: Period 120us, Pulse 50us (Tests asynchronous press)

V_ACT_L ACT_L 0 PULSE(0 5 10u 1u 1u 50u 120u)

S1 VCC BTN_L ACT_L 0 SW_IDEAL

R1 BTN_L 0 10k

* S2: Right Safety Switch (Pushbutton NO)

* Connects VCC to BTN_R when pressed.

* Pulse Pattern: Period 100us, Pulse 50us

V_ACT_R ACT_R 0 PULSE(0 5 20u 1u 1u 50u 100u)

S2 VCC BTN_R ACT_R 0 SW_IDEAL

R2 BTN_R 0 10k

* ==============================================================================

* LOGIC STAGE (U1: 74HC00 Quad NAND)

* ==============================================================================

* Implementing logic using Behavioral Voltage Sources (B-Sources) with continuous

* sigmoid functions for convergence robustness.

* Logic High = 5V, Logic Low = 0V. Threshold ~ 2.5V.

* U1 Gate 1: Inputs BTN_L (Pin 1), BTN_R (Pin 2) -> Output NAND_INTER (Pin 3)

* Function: NAND(BTN_L, BTN_R)

B_U1_G1 NAND_INTER 0 V=5 * (1 - ( (1/(1+exp(-20*(V(BTN_L)-2.5)))) * (1/(1+exp(-20*(V(BTN_R)-2.5)))) ))

* U1 Gate 2: Inputs NAND_INTER (Pin 4, 5) -> Output LOGIC_OUT (Pin 6)

* Function: NAND(NAND_INTER, NAND_INTER) = NOT(NAND_INTER)

* Combined Function: AND(BTN_L, BTN_R)

B_U1_G2 LOGIC_OUT 0 V=5 * (1 - ( (1/(1+exp(-20*(V(NAND_INTER)-2.5)))) * (1/(1+exp(-20*(V(NAND_INTER)-2.5)))) ))

* ==============================================================================

* OUTPUT DRIVER STAGE

* ==============================================================================

* R3: Base current limiting

R3 LOGIC_OUT BASE 1k

* Q1: 2N2222 Relay Driver

* Emitter to GND, Collector to RELAY_COIL_LO

Q1 RELAY_COIL_LO BASE 0 2N2222MOD

* ==============================================================================

* RELAY STAGE (K1)

* ==============================================================================

* Relay Coil Configuration:

* Connected between VCC and RELAY_COIL_LO.

* Modeled as Inductor + Series Resistor.

L_K1 VCC K1_NODE 10m

R_K1 K1_NODE RELAY_COIL_LO 100

* D1: Flyback Diode (1N4007)

* Anode to RELAY_COIL_LO, Cathode to VCC (Reverse biased)

D1 RELAY_COIL_LO VCC D1N4007

* Relay Contact (Switch):

* Logic: Switch closes when Coil is energized.

* Coil is energized when Q1 is ON (RELAY_COIL_LO is Low).

* Control Voltage = V(VCC) - V(RELAY_COIL_LO).

* If Q1 ON: 5V - 0.2V = 4.8V (> 2.5V Threshold) -> Switch CLOSED.

* If Q1 OFF: 5V - 5V = 0V (< 2.5V Threshold) -> Switch OPEN.

B_K1_CTRL K1_CTRL 0 V = V(VCC) - V(RELAY_COIL_LO)

S_K1 V_MOTOR_RAIL MOTOR_POS K1_CTRL 0 SW_IDEAL

* ==============================================================================

* LOAD (Motor M1)

* ==============================================================================

* M1: 12V DC Motor connected between MOTOR_POS and 0

* Modeled as Resistor + Inductor

R_M1 MOTOR_POS M1_INT 20

L_M1 M1_INT 0 5m

* ==============================================================================

* ANALYSIS COMMANDS

* ==============================================================================

.op

* Transient analysis: 1us step, 500us total time

.tran 1u 500u

* Print results for batch processing

* Inputs: BTN_L, BTN_R

* Output: MOTOR_POS (Load Voltage)

* Debug: LOGIC_OUT, RELAY_COIL_LO

.print tran V(BTN_L) V(BTN_R) V(MOTOR_POS) V(LOGIC_OUT) V(RELAY_COIL_LO) I(L_M1)

.endResultados de Simulación (Transitorio)

Show raw data table (1202 rows)

Index time v(btn_l) v(btn_r) v(motor_pos) v(logic_out) v(relay_coil_lo l_m1#branch 0 0.000000e+00 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 1 1.000000e-08 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 2 2.000000e-08 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 3 4.000000e-08 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 4 8.000000e-08 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 5 1.600000e-07 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 6 3.200000e-07 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 7 6.400000e-07 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 8 1.280000e-06 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 9 2.280000e-06 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 10 3.280000e-06 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 11 4.280000e-06 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 12 5.280000e-06 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 13 6.280000e-06 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 14 7.280000e-06 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 15 8.280000e-06 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 16 9.280000e-06 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 17 1.000000e-05 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 18 1.010000e-05 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 19 1.027500e-05 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 20 1.032344e-05 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 21 1.040820e-05 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 22 1.043167e-05 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 23 1.047272e-05 4.995005e-03 4.995005e-03 2.399995e-05 -6.01853e-36 5.000000e+00 1.199998e-06 ... (1178 more rows) ...

Errores comunes y cómo evitarlos

- Entradas flotantes: Olvidar R1 o R2 provoca que las entradas de la puerta NAND queden flotantes, a menudo leyéndose como «Alto» debido al ruido. Solución: Asegúrate de que las resistencias pull-down estén firmemente conectadas a Tierra.

- Falta del diodo flyback: Omitir D1 crea picos de voltaje cuando el relé se apaga, lo que puede destruir Q1 o reiniciar el chip lógico. Solución: Coloca siempre un diodo a través de la bobina del relé (Cátodo al positivo).

- Accionamiento directo: Intentar accionar el motor o el relé directamente desde el pin de salida del 74HC00. Solución: Utiliza siempre un transistor (Q1) para amplificar la corriente para cargas inductivas como relés.

Solución de problemas

- El motor funciona inmediatamente al encender: Comprueba si S1 o S2 están cableados como Normalmente Cerrados en lugar de Normalmente Abiertos, o si el transistor Q1 está en cortocircuito.

- El relé hace clic pero el motor no funciona: Comprueba la fuente de alimentación V2 y las conexiones en los contactos del relé (COM y NO).

- La lógica funciona pero se calienta: Comprueba si VCC (Pin 14) y GND (Pin 7) están invertidos. Desconecta la alimentación inmediatamente.

- Comportamiento errático: Añade un condensador de desacoplo de 100 nF entre el Pin 14 y el Pin 7 del CI, cerca del chip.

Posibles mejoras y extensiones

- Parada de emergencia: Añade un botón de enclavamiento Normalmente Cerrado (NC) en serie con la bobina del relé o la resistencia de base R3 para cortar la alimentación instantáneamente independientemente del estado lógico.

- Retroalimentación visual: Añade un LED verde (con una resistencia de 330 Ω) conectado al nodo

LOGIC_OUTpara indicar cuándo se cumple la condición de seguridad, incluso si la alimentación del motor (V2) está apagada.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.