Nivel: Avanzado. Diseñe un sistema de seguridad redundante que permita la inyección de catalizador solo cuando tres variables críticas estén dentro del rango.

Objetivo y caso de uso

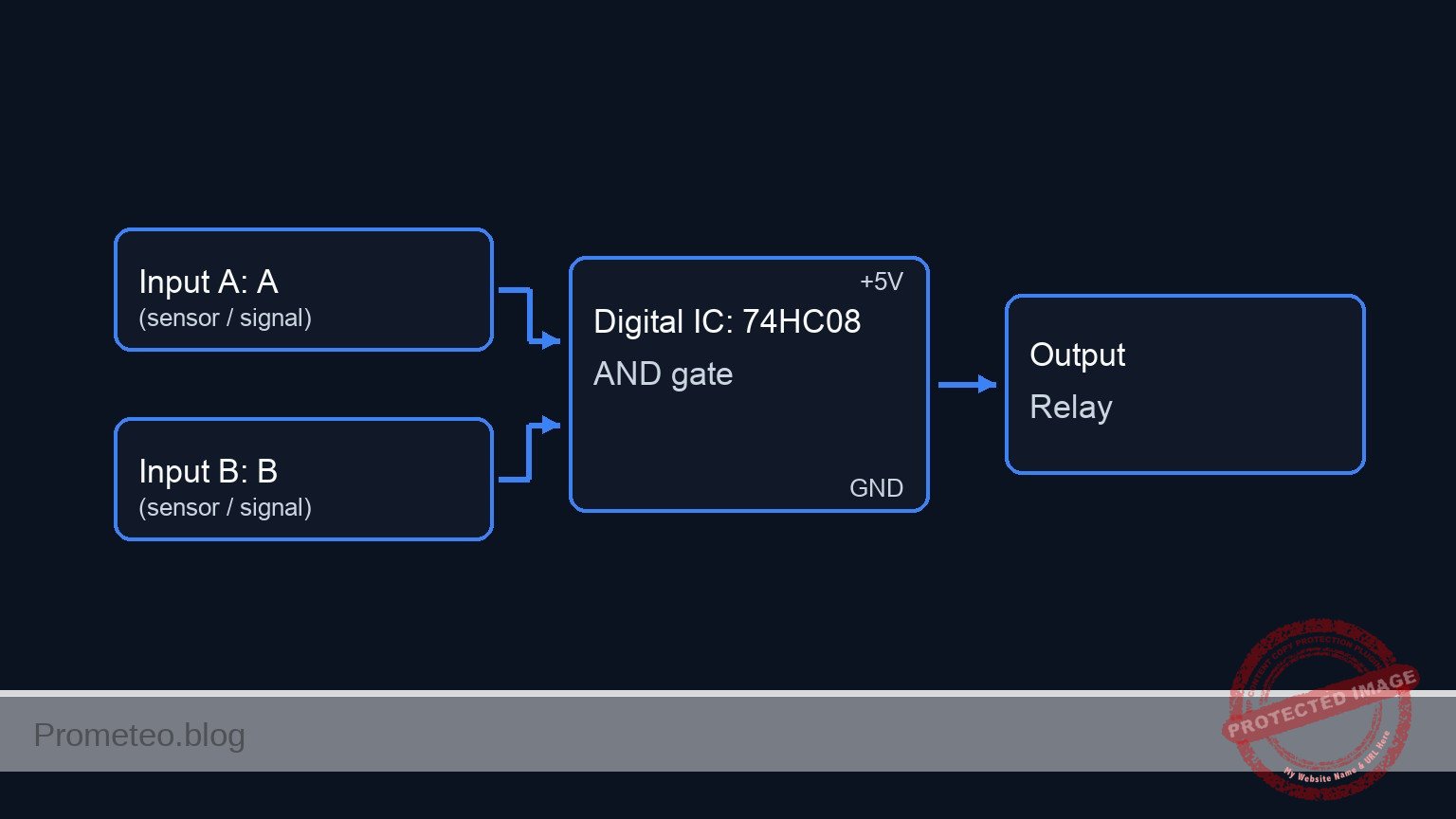

En este caso, construirá un circuito lógico de enclavamiento de seguridad basado en hardware que monitorea tres parámetros analógicos simulados (Temperatura, Presión, Nivel). Utiliza comparadores para digitalizar estas señales y una disposición de puertas lógicas en cascada para controlar un relé de alta potencia.

Por qué es útil:

* Seguridad industrial: Evita que las reacciones químicas comiencen a menos que las condiciones ambientales sean perfectas, evitando eventos térmicos descontrolados.

* Protección de maquinaria: Asegura que las guardas estén cerradas, la presión liberada y los motores detenidos antes de desbloquear las puertas de mantenimiento.

* Dispositivos médicos: Evita la emisión de láser o radiación a menos que todos los enclavamientos (llave, contacto de puerta, sensor de paciente) estén activos.

Resultado esperado:

* Salida lógica: La señal de control final V_SAFE pasa a ALTO (Lógica 1, ~5V) solo cuando las tres entradas están dentro de la zona «Segura» simultáneamente.

* Indicación visual: El relé se activa (cerrando el circuito para la válvula de catalizador) y un LED verde se enciende solo en el estado 1-1-1.

* Histéresis: El sistema mantiene la estabilidad cerca de los umbrales de conmutación (dependiendo de la configuración del comparador).

Público objetivo: Estudiantes de ingeniería electrónica y técnicos de automatización industrial.

Materiales

- V1: Fuente de alimentación de 5 V CC, función: Alimentación lógica y de sensores.

- U1: 74HC08, función: Cuádruple puerta AND de 2 entradas (usada para crear lógica de 3 entradas).

- U2: LM339, función: Cuádruple comparador de colector abierto (digitaliza sensores analógicos).

- R1: Potenciómetro de 10 kΩ, función: Simulador para Sensor de Temperatura.

- R2: Potenciómetro de 10 kΩ, función: Simulador para Sensor de Presión.

- R3: Potenciómetro de 10 kΩ, función: Simulador para Nivel de Tanque.

- R_REF: Arreglo de resistencias de 10 kΩ (o potenciómetros), función: Divisores de voltaje para umbrales de referencia (2.5 V).

- R_PU1: Resistencia de 4.7 kΩ, función: Pull-up para la salida del Comparador 1.

- R_PU2: Resistencia de 4.7 kΩ, función: Pull-up para la salida del Comparador 2.

- R_PU3: Resistencia de 4.7 kΩ, función: Pull-up para la salida del Comparador 3.

- R_BASE: Resistencia de 1 kΩ, función: Limitación de corriente de base del transistor.

- Q1: Transistor NPN 2N2222, función: Controlador del relé.

- K1: Relé de 5 V, función: Actuador para la válvula de catalizador.

- D1: Diodo 1N4007, función: Protección flyback para Q1.

- D2: LED verde, función: Indicador para «Inyección Activa».

- R_LED: Resistencia de 330 Ω, función: Limitación de corriente del LED.

Pin-out del CI utilizado

Chip seleccionado: 74HC08 (Cuádruple puerta AND de 2 entradas)

| Pin | Nombre | Función lógica | Conexión en este caso |

|---|---|---|---|

| 1 | 1A | Entrada A (Puerta 1) | Conectado al Estado de Temperatura (SIG_TEMP) |

| 2 | 1B | Entrada B (Puerta 1) | Conectado al Estado de Presión (SIG_PRES) |

| 3 | 1Y | Salida (Puerta 1) | Resultado intermedio (Temp AND Pres) |

| 4 | 2A | Entrada A (Puerta 2) | Conectado a 1Y (Resultado intermedio) |

| 5 | 2B | Entrada B (Puerta 2) | Conectado al Estado de Nivel (SIG_LEV) |

| 6 | 2Y | Salida (Puerta 2) | Señal de Seguridad Final (V_SAFE) |

| 7 | GND | Tierra | Conectado a la fuente de alimentación 0 |

| 14 | VCC | Alimentación | Conectado a VCC (+5V) |

Guía de conexionado

Fuente de alimentación

* V1 se conecta entre VCC y 0 (GND).

* U1 (74HC08) Pin 14 se conecta a VCC, Pin 7 a 0.

* U2 (LM339) Pin 3 (V+) se conecta a VCC, Pin 12 (GND) a 0.

Entradas analógicas y comparadores (Acondicionamiento de señal)

* R1 (Potenciómetro de Temp) se conecta entre VCC y 0; el cursor se conecta a U2 Entrada 1- (NODE_T_SENS).

* El divisor de referencia se conecta a U2 Entrada 1+ (NODE_REF).

* U2 Salida 1 se conecta a SIG_TEMP.

* R_PU1 se conecta entre VCC y SIG_TEMP (requerido para colector abierto).

* R2 (Potenciómetro de Pres) se conecta entre VCC y 0; el cursor se conecta a U2 Entrada 2- (NODE_P_SENS).

* El divisor de referencia se conecta a U2 Entrada 2+ (NODE_REF).

* U2 Salida 2 se conecta a SIG_PRES.

* R_PU2 se conecta entre VCC y SIG_PRES.

* R3 (Potenciómetro de Nivel) se conecta entre VCC y 0; el cursor se conecta a U2 Entrada 3- (NODE_L_SENS).

* El divisor de referencia se conecta a U2 Entrada 3+ (NODE_REF).

* U2 Salida 13 se conecta a SIG_LEV.

* R_PU3 se conecta entre VCC y SIG_LEV.

Lógica digital (Cascada para AND de 3 entradas)

* U1 Pin 1 (1A) se conecta a SIG_TEMP.

* U1 Pin 2 (1B) se conecta a SIG_PRES.

* U1 Pin 3 (1Y) se conecta a U1 Pin 4 (2A).

* U1 Pin 5 (2B) se conecta a SIG_LEV.

* U1 Pin 6 (2Y) se conecta a V_SAFE.

Etapa de salida

* R_BASE se conecta entre V_SAFE y NODE_BASE.

* La Base de Q1 se conecta a NODE_BASE.

* El Emisor de Q1 se conecta a 0.

* El Colector de Q1 se conecta a NODE_RELAY.

* K1 (Bobina del relé) se conecta entre VCC y NODE_RELAY.

* D1 se conecta entre NODE_RELAY (Ánodo) y VCC (Cátodo) Nota: Verifique la polaridad, cátodo al positivo para flyback.

* R_LED se conecta entre NODE_RELAY y NODE_LED_A.

* D2 se conecta entre NODE_LED_A y 0.

Diagrama de bloques conceptual

Esquemático

Title: Practical case: Safety interlock in a chemical reactor

[ SENSORS / INPUTS ] [ SIGNAL CONDITIONING ] [ LOGIC PROCESSING ] [ OUTPUT ACTUATOR STAGE ]

(VCC / Pull-ups) (VCC 5V Source)

| |

[ R1: Temp Pot ] --(Analog)--> [ U2: LM339 Comp 1 ] --(SIG_TEMP)-->+ +------------+------------+

(Simulates Sensor) [ Ref: 2.5V Divider] | | | |

v [ K1 Relay ] [ D1 Diode ] [ R_LED ]

[ U1: 74HC08 ] [ Coil ] [ Cathode^ ] [ + ]

[ R2: Pres Pot ] --(Analog)--> [ U2: LM339 Comp 2 ] --(SIG_PRES)-->[ AND Gate A ] --(Intermed)--> | [ Anode v ] [ D2 LED ]

(Simulates Sensor) [ Ref: 2.5V Divider] [ ] | | | |

| +------------+------------+

v |

[ U1: 74HC08 ] | (NODE_RELAY)

[ AND Gate B ] v

[ R3: Levl Pot ] --(Analog)--> [ U2: LM339 Comp 3 ] --(SIG_LEV)--->(Pin 5)--------->[ ] --(V_SAFE)--> [ R_BASE ] --> [ Q1: 2N2222 ]

(Simulates Sensor) [ Ref: 2.5V Divider] [ ] [ NPN Base ]

[ ]

[ Collector ] --< (Sinks Current)

[ Emitter ]

|

GND

Tabla de verdad

Esta tabla representa la lógica en cascada (Temp AND Presión AND Nivel).

| Temp OK (A) | Pres OK (B) | Nivel OK (C) | Intermedio (A·B) | Salida Final (V_SAFE) | Acción |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | Modo seguro (Apagado) |

| 0 | 0 | 1 | 0 | 0 | Modo seguro (Apagado) |

| 0 | 1 | 0 | 0 | 0 | Modo seguro (Apagado) |

| 0 | 1 | 1 | 0 | 0 | Modo seguro (Apagado) |

| 1 | 0 | 0 | 0 | 0 | Modo seguro (Apagado) |

| 1 | 0 | 1 | 0 | 0 | Modo seguro (Apagado) |

| 1 | 1 | 0 | 1 | 0 | Modo seguro (Apagado) |

| 1 | 1 | 1 | 1 | 1 | Inyectar catalizador |

Mediciones y pruebas

- Prueba de sensor individual: Ajuste R1 (Temp) por debajo del umbral. Verifique que

SIG_TEMPpase a ALTO (aprox 5V). Repita para R2 y R3. - Validación de la lógica: Establezca Temp y Presión en «Seguro» (Lógica alta), pero Nivel en «Inseguro» (Lógica baja). Mida U1 Pin 3 (Intermedio); debería estar en ALTO. Mida U1 Pin 6 (

V_SAFE); debería estar en BAJO. - Activación completa: Establezca los tres potenciómetros en el rango «Seguro». Verifique que

V_SAFEesté en ALTO, Q1 se sature y el Relé (K1) haga clic en «Encendido». - Tiempo de respuesta: Conecte el canal 1 de un osciloscopio a

SIG_LEVy el canal 2 aV_SAFE. Conmute el interruptor de Nivel y mida el retardo de propagación (típicamente nanosegundos para la puerta, milisegundos para el relé).

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Practical case: Safety interlock in a chemical reactor

* --- Models ---

* Generic NPN Transistor

.model 2N2222MOD NPN(IS=1E-14 VAF=100 BF=200 IKF=0.3 XTB=1.5 BR=3 CJC=8E-12 CJE=25E-12 TR=46.91E-9 TF=411.1E-12 ITF=0.6 VTF=1.7 XTF=3 RB=10 RC=1 RE=0.1)

* Flyback Diode

.model D1N4007 D(IS=7.02767n RS=0.03415 N=1.2686 EG=1.11 XTI=3 BV=1000 IBV=10m CJO=10p VJ=0.7 M=0.5 FC=0.5 TT=100n)

* Green LED Indicator

.model LED_GREEN D(IS=1e-22 RS=5 N=1.5 CJO=50p BV=5 IBV=10u EG=2.1)

* Voltage Controlled Switch for Open Collector Comparator

* Vt=0: Switch state changes when control voltage crosses 0V

* Ron=10: Low resistance when closed (Logic 0 / Low)

* Roff=100Meg: High resistance when open (Logic 1 / High via Pull-up)

.model SW_OC SW(Vt=0 Vh=0.001 Ron=10 Roff=100Meg)

* --- Power Supply ---

* V1: 5 V DC power supply

V1 VCC 0 DC 5

* --- Reference Voltage (R_REF) ---

* Function: Voltage dividers for reference thresholds (2.5 V)

* Wiring: Reference divider connects to U2 Input + (NODE_REF)

R_REF_A VCC NODE_REF 10k

R_REF_B NODE_REF 0 10k

* --- Sensors (Simulated with PWL Voltage Sources) ---

* R1, R2, R3 Potentiometers simulated by PWL sources at the wiper nodes.

* Logic: Low Voltage (<2.5V) = Safe. High Voltage (>2.5V) = Unsafe/Alarm.

* Sequence: T=Safe, then Temp Fault, then Pres Fault, then Level Fault.

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Practical case: Safety interlock in a chemical reactor

* --- Models ---

* Generic NPN Transistor

.model 2N2222MOD NPN(IS=1E-14 VAF=100 BF=200 IKF=0.3 XTB=1.5 BR=3 CJC=8E-12 CJE=25E-12 TR=46.91E-9 TF=411.1E-12 ITF=0.6 VTF=1.7 XTF=3 RB=10 RC=1 RE=0.1)

* Flyback Diode

.model D1N4007 D(IS=7.02767n RS=0.03415 N=1.2686 EG=1.11 XTI=3 BV=1000 IBV=10m CJO=10p VJ=0.7 M=0.5 FC=0.5 TT=100n)

* Green LED Indicator

.model LED_GREEN D(IS=1e-22 RS=5 N=1.5 CJO=50p BV=5 IBV=10u EG=2.1)

* Voltage Controlled Switch for Open Collector Comparator

* Vt=0: Switch state changes when control voltage crosses 0V

* Ron=10: Low resistance when closed (Logic 0 / Low)

* Roff=100Meg: High resistance when open (Logic 1 / High via Pull-up)

.model SW_OC SW(Vt=0 Vh=0.001 Ron=10 Roff=100Meg)

* --- Power Supply ---

* V1: 5 V DC power supply

V1 VCC 0 DC 5

* --- Reference Voltage (R_REF) ---

* Function: Voltage dividers for reference thresholds (2.5 V)

* Wiring: Reference divider connects to U2 Input + (NODE_REF)

R_REF_A VCC NODE_REF 10k

R_REF_B NODE_REF 0 10k

* --- Sensors (Simulated with PWL Voltage Sources) ---

* R1, R2, R3 Potentiometers simulated by PWL sources at the wiper nodes.

* Logic: Low Voltage (<2.5V) = Safe. High Voltage (>2.5V) = Unsafe/Alarm.

* Sequence: T=Safe, then Temp Fault, then Pres Fault, then Level Fault.

* R1: Temp Sensor Simulator

V_SENS_T NODE_T_SENS 0 PWL(0 1 100u 1 101u 4 200u 4 201u 1)

* R2: Pressure Sensor Simulator

V_SENS_P NODE_P_SENS 0 PWL(0 1 300u 1 301u 4 400u 4 401u 1)

* R3: Tank Level Simulator

V_SENS_L NODE_L_SENS 0 PWL(0 1 500u 1 501u 4 600u 4 601u 1)

* --- U2: LM339 Quad Comparator ---

* Function: Digitizes analog sensors. Open Collector Outputs.

* Logic: If V(In-) > V(In+), Switch closes to Ground (Output Low).

* Else Switch opens (Output High via Pull-up).

* Comparator 1 (Temperature)

* Wiring: Wiper (NODE_T_SENS) to Input 1-, Ref to Input 1+, Output to SIG_TEMP

S_COMP1 SIG_TEMP 0 NODE_T_SENS NODE_REF SW_OC

* R_PU1: Pull-up for Comparator 1

R_PU1 VCC SIG_TEMP 4.7k

* Comparator 2 (Pressure)

* Wiring: Wiper (NODE_P_SENS) to Input 2-, Ref to Input 2+, Output to SIG_PRES

S_COMP2 SIG_PRES 0 NODE_P_SENS NODE_REF SW_OC

* R_PU2: Pull-up for Comparator 2

R_PU2 VCC SIG_PRES 4.7k

* Comparator 3 (Level)

* Wiring: Wiper (NODE_L_SENS) to Input 3-, Ref to Input 3+, Output to SIG_LEV

S_COMP3 SIG_LEV 0 NODE_L_SENS NODE_REF SW_OC

* R_PU3: Pull-up for Comparator 3

R_PU3 VCC SIG_LEV 4.7k

* --- U1: 74HC08 Quad 2-input AND ---

* Function: Safety Logic.

* Modeled using Behavioral Sources (Sigmoid function for HC logic levels).

* Gate 1 (Pins 1, 2, 3)

* Inputs: SIG_TEMP, SIG_PRES. Output: NODE_AND_INT

B_AND1 NODE_AND_INT 0 V = 5 * (1 / (1 + exp(-20*(V(SIG_TEMP)-2.5)))) * (1 / (1 + exp(-20*(V(SIG_PRES)-2.5))))

* Gate 2 (Pins 4, 5, 6)

* Inputs: NODE_AND_INT (Pin 4 connects to Pin 3), SIG_LEV. Output: V_SAFE

B_AND2 V_SAFE 0 V = 5 * (1 / (1 + exp(-20*(V(NODE_AND_INT)-2.5)))) * (1 / (1 + exp(-20*(V(SIG_LEV)-2.5))))

* --- Output Stage ---

* R_BASE: Transistor base current limiting

R_BASE V_SAFE NODE_BASE 1k

* Q1: 2N2222 NPN Transistor, Relay driver

* Wiring: Base to NODE_BASE, Emitter to 0, Collector to NODE_RELAY

Q1 NODE_RELAY NODE_BASE 0 2N2222MOD

* K1: 5 V Relay Coil

* Wiring: Connects between VCC and NODE_RELAY

* Modeled as Inductor and Series Resistor

L_K1 VCC NODE_RELAY_INT 10m

R_K1 NODE_RELAY_INT NODE_RELAY 100

* D1: Flyback protection

* Wiring: Anode to NODE_RELAY, Cathode to VCC

D1 NODE_RELAY VCC D1N4007

* D2 & R_LED: Indicator "Injection Active"

* Corrected Wiring: LED should be parallel to Relay Coil to indicate Activation.

* Path: VCC -> Resistor -> LED Anode -> LED Cathode -> Collector (NODE_RELAY).

* When Q1 is ON (Relay Active), NODE_RELAY is Low (~0.2V), LED turns ON.

R_LED VCC NODE_LED_A 330

D2 NODE_LED_A NODE_RELAY LED_GREEN

* --- Analysis Directives ---

* Transient analysis to observe the sequence of sensor faults

.tran 1u 800u

* Print required signals

.print tran V(NODE_T_SENS) V(NODE_P_SENS) V(NODE_L_SENS)

.print tran V(SIG_TEMP) V(SIG_PRES) V(SIG_LEV)

.print tran V(NODE_AND_INT) V(V_SAFE)

.print tran V(NODE_RELAY) V(NODE_BASE)

.endResultados de Simulación (Transitorio)

Show raw data table (3828 rows)

Index time v(node_t_sens) v(node_p_sens) v(node_l_sens) 0 0.000000e+00 1.000000e+00 1.000000e+00 1.000000e+00 1 1.000000e-08 1.000000e+00 1.000000e+00 1.000000e+00 2 2.000000e-08 1.000000e+00 1.000000e+00 1.000000e+00 3 4.000000e-08 1.000000e+00 1.000000e+00 1.000000e+00 4 8.000000e-08 1.000000e+00 1.000000e+00 1.000000e+00 5 1.600000e-07 1.000000e+00 1.000000e+00 1.000000e+00 6 3.200000e-07 1.000000e+00 1.000000e+00 1.000000e+00 7 6.400000e-07 1.000000e+00 1.000000e+00 1.000000e+00 8 1.280000e-06 1.000000e+00 1.000000e+00 1.000000e+00 9 2.280000e-06 1.000000e+00 1.000000e+00 1.000000e+00 10 3.280000e-06 1.000000e+00 1.000000e+00 1.000000e+00 11 4.280000e-06 1.000000e+00 1.000000e+00 1.000000e+00 12 5.280000e-06 1.000000e+00 1.000000e+00 1.000000e+00 13 6.280000e-06 1.000000e+00 1.000000e+00 1.000000e+00 14 7.280000e-06 1.000000e+00 1.000000e+00 1.000000e+00 15 8.280000e-06 1.000000e+00 1.000000e+00 1.000000e+00 16 9.280000e-06 1.000000e+00 1.000000e+00 1.000000e+00 17 1.028000e-05 1.000000e+00 1.000000e+00 1.000000e+00 18 1.128000e-05 1.000000e+00 1.000000e+00 1.000000e+00 19 1.228000e-05 1.000000e+00 1.000000e+00 1.000000e+00 20 1.328000e-05 1.000000e+00 1.000000e+00 1.000000e+00 21 1.428000e-05 1.000000e+00 1.000000e+00 1.000000e+00 22 1.528000e-05 1.000000e+00 1.000000e+00 1.000000e+00 23 1.628000e-05 1.000000e+00 1.000000e+00 1.000000e+00 ... (3804 more rows) ...

Errores comunes y cómo evitarlos

- Faltan resistencias pull-up: El comparador LM339 tiene una salida de colector abierto. Si olvida R_PU1/2/3, las entradas de la puerta lógica flotarán o permanecerán en BAJO. Siempre ate las salidas a VCC a través de una resistencia (p. ej., 4.7kΩ).

- Entradas no utilizadas flotantes: El 74HC08 es un dispositivo CMOS. Si los pines 9, 10, 12, 13 (Puertas 3 y 4) se dejan flotando, captan ruido y aumentan el consumo de energía. Conecte las entradas no utilizadas a GND.

- Patada inductiva (Kickback): Omitir D1 (diodo flyback) a través de la bobina del relé. Esto generará un pico de alto voltaje cuando el relé se apague, destruyendo el transistor Q1 inmediatamente.

Solución de problemas

- El relé vibra (sonido de zumbido): Las entradas analógicas oscilan exactamente en el voltaje umbral. Solución: Agregue una resistencia de retroalimentación (histéresis) entre la salida del comparador y la entrada no inversora.

- La salida lógica siempre está en ALTO: Verifique las entradas del comparador. Si el voltaje de referencia está invertido (p. ej., Ref > Señal vs Señal > Ref), la lógica podría estar invertida.

- El transistor se calienta pero el relé no conmuta: Q1 podría estar recibiendo insuficiente corriente de base, o el pinout (E-B-C) es incorrecto. Solución: Verifique el valor de R_BASE y el pinout del transistor.

Posibles mejoras y extensiones

- Circuito de enclavamiento (Latch): Agregue un bucle de retroalimentación (o un latch Set-Reset) para que si se viola la seguridad, el sistema se apague y requiera presionar un botón de «Reset» manual para reiniciar, incluso si las condiciones vuelven a la normalidad.

- Identificación de fallas: Agregue LEDs rojos a la salida de cada comparador (invertidos) para indicar exactamente qué variable (Temperatura, Presión o Nivel) causó el apagado.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.