Nivel: Básico

Implemente un circuito lógico donde una propuesta se aprueba solo si dos miembros votan «Sí» y un tercer miembro otorga su aprobación (sin veto), utilizando un único CI 74HC00.

Objetivo y caso de uso

En este caso práctico, construirá un circuito de toma de decisiones utilizando lógica digital. El sistema representa un comité donde el Miembro A y el Miembro B deben votar a favor para que se apruebe una moción, pero el Miembro C (el Presidente) posee una «Llave de autorización». Si el Miembro C no activa su interruptor (Lógica Baja), el voto es vetado independientemente de A y B.

- Gobierno corporativo: Modela una junta directiva donde se necesita el apoyo de la mayoría, pero el CEO tiene la aprobación final.

- Enclavamientos de seguridad: Representa una prensa mecánica donde dos operadores deben presionar botones (A y B), pero se debe insertar una llave de Habilitación Maestra (C) para que la máquina funcione.

- Acceso de seguridad: Requiere dos llaves de usuario distintas más una señal de autorización del servidor central.

Resultado esperado:

* Salida Alta (LED ENCENDIDO): Solo cuando la Entrada A es Alta, la Entrada B es Alta Y la Entrada C es Alta.

* Salida Baja (LED APAGADO): Cualquier otra combinación (por ejemplo, si A o B votan «No», o si C ejerce el veto poniendo su entrada en Bajo).

* Público objetivo: Estudiantes y aficionados que aprenden a construir funciones lógicas complejas (AND de 3 entradas) utilizando puertas NAND universales.

Materiales

- U1: 74HC00 (Cuádruple puerta NAND de 2 entradas)

- SW1: Interruptor DIP de 3 posiciones (o tres interruptores SPST individuales), función: Entradas A, B y C

- R1: Resistencia de 10 kΩ, función: pull-down para la Entrada A

- R2: Resistencia de 10 kΩ, función: pull-down para la Entrada B

- R3: Resistencia de 10 kΩ, función: pull-down para la Entrada C

- R4: Resistencia de 330 Ω, función: limitación de corriente del LED

- D1: LED rojo, función: Indicador de salida lógica

- V1: Fuente de alimentación de 5 V CC

Pin-out del CI utilizado

Chip: 74HC00 (Cuádruple NAND de 2 entradas)

Este proyecto utiliza las cuatro puertas dentro del chip para crear una función AND de 3 entradas (Y = A · B · C).

| Pin | Nombre | Función lógica | Conexión en este caso |

|---|---|---|---|

| 1 | 1 A | Entrada | Conectar al Interruptor A |

| 2 | 1B | Entrada | Conectar al Interruptor B |

| 3 | 1Y | Salida | Salida de la Puerta 1 (\overlineA · B) |

| 4 | 2 A | Entrada | Conectar al Pin 3 (1Y) |

| 5 | 2B | Entrada | Conectar al Pin 3 (1Y) |

| 6 | 2Y | Salida | Salida de la Puerta 2 (1Y invertida \to A · B) |

| 7 | GND | Tierra | Conectar a la Fuente de Alimentación 0 V |

| 8 | 3Y | Salida | Salida de la Puerta 3 (\overline(A · B) · C) |

| 9 | 3 A | Entrada | Conectar al Interruptor C |

| 10 | 3B | Entrada | Conectar al Pin 6 (2Y) |

| 11 | 4Y | Salida | Salida final (controla el LED) |

| 12 | 4 A | Entrada | Conectar al Pin 8 (3Y) |

| 13 | 4B | Entrada | Conectar al Pin 8 (3Y) |

| 14 | VCC | Alimentación | Conectar a +5 V |

Guía de conexionado

- VCC: Conectar el terminal positivo de

V1, el pin 14 deU1y el lado común deSW1. - GND: Conectar el terminal negativo de

V1, el pin 7 deU1,R1(parte inferior),R2(parte inferior),R3(parte inferior) yD1(cátodo). - Input_A: Conectar

SW1(Interruptor 1) aR1(parte superior) y al pin 1 deU1. - Input_B: Conectar

SW1(Interruptor 2) aR2(parte superior) y al pin 2 deU1. - Input_C (Veto): Conectar

SW1(Interruptor 3) aR3(parte superior) y al pin 9 deU1. - Node_NAND1: Conectar el pin 3 de

U1(Salida 1) al pin 4 deU1y al pin 5 deU1(Entradas de la Puerta 2). - Node_AND_AB: Conectar el pin 6 de

U1(Salida 2) al pin 10 deU1(Entrada de la Puerta 3). - Node_NAND_FINAL: Conectar el pin 8 de

U1(Salida 3) al pin 12 deU1y al pin 13 deU1(Entradas de la Puerta 4). - Vout: Conectar el pin 11 de

U1(Salida Final) aR4(un lado). - LED_Anode: Conectar

R4(el otro lado) aD1(ánodo).

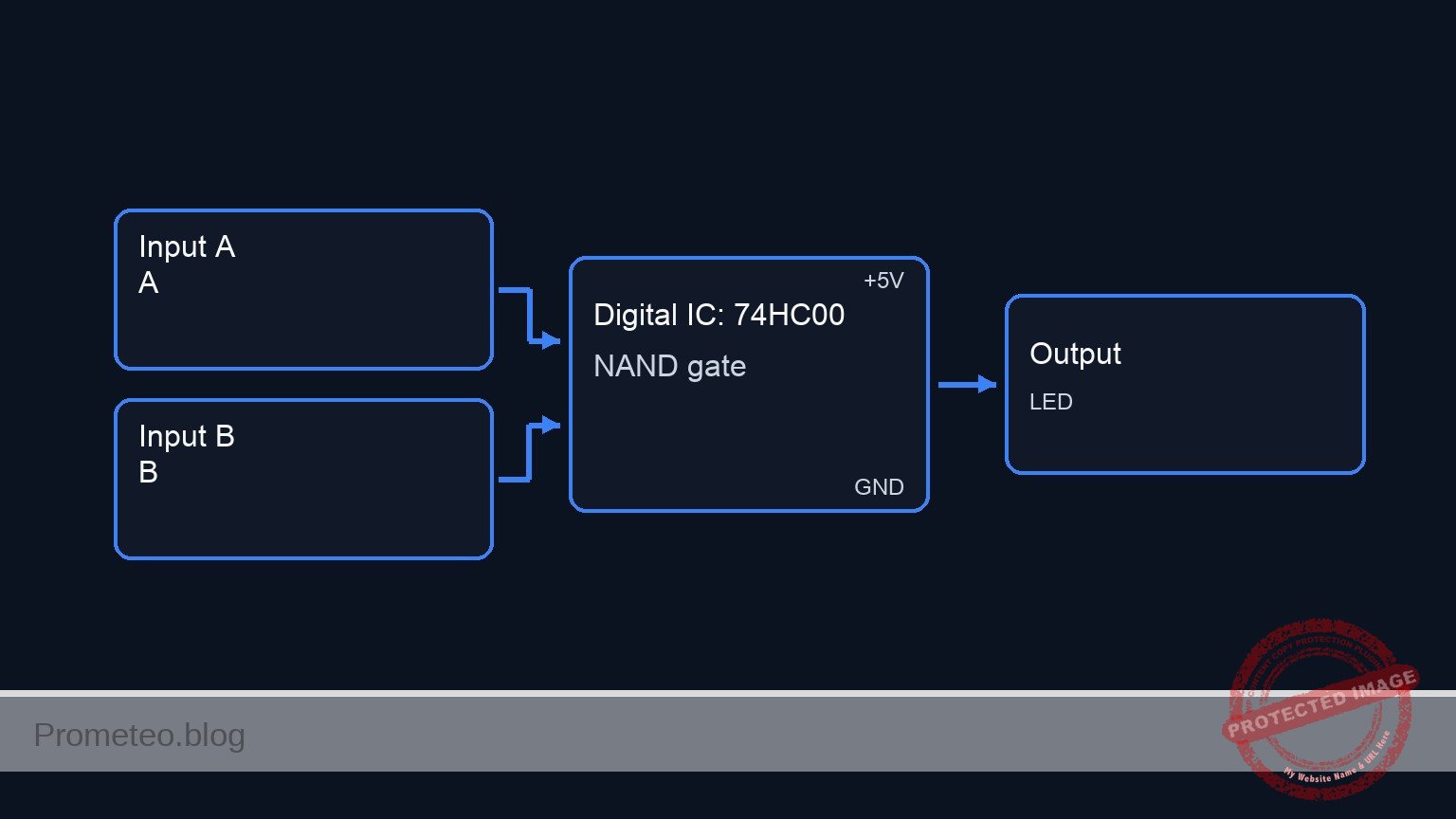

Diagrama de bloques conceptual

Esquemático

Practical Case: Veto Voting System (74HC00 Logic Flow)

INPUTS (Active High) LOGIC PROCESSING (74HC00 Quad NAND) OUTPUT

=======================================================================================================

[ SW A + R1 ] --(Pin 1)-->+

|

[ U1: Gate 1 ] --(Pin 3)--> [ U1: Gate 2 ] --(Pin 6)---+

[ 2-In NAND ] [ NAND as NOT] |

| (Pins 4+5) |

[ SW B + R2 ] --(Pin 2)-->+ |

|

v

[ U1: Gate 3 ] --(Pin 8)--> [ U1: Gate 4 ] --(Pin 11)--> [ R4: 330R ] --> [ D1: LED ] --> GND

[ 2-In NAND ] [ NAND as NOT]

(Pin 10) \ (Pins 12+13)

\

[ SW C + R3 ] -------------------------------------------------------(Pin 9)---------+

(Veto/Enable)

=======================================================================================================

Logic Summary:

1. Gate 1 & 2 form an AND gate for Inputs A & B.

2. Gate 3 & 4 form an AND gate for (Result of A/B) & Input C.

3. Final Function: LED turns ON only if A AND B AND C are all High.

Tabla de verdad

El circuito implementa la función lógica Y = A · B · C.

* A/B: Votantes

* C: Presidente/Autorización (0 = Veto/Bloqueo, 1 = Permitir)

| Entrada A (Votante 1) | Entrada B (Votante 2) | Entrada C (Autorización) | Salida Y (LED) | Resultado |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | Fallo |

| 0 | 1 | 1 | 0 | Fallo (Falta de votos) |

| 1 | 0 | 1 | 0 | Fallo (Falta de votos) |

| 1 | 1 | 0 | 0 | VETADO |

| 1 | 1 | 1 | 1 | Aprobado |

Mediciones y pruebas

- Verificación de alimentación: Antes de insertar el CI, verifique 5 V entre las líneas VCC y GND en su protoboard.

- Estado predeterminado: Asegúrese de que todos los interruptores estén en OFF (apagados). Encienda la alimentación. El LED debe estar APAGADO.

- Prueba de veto: Ponga el Interruptor A y el Interruptor B en ON (Alto). Mantenga el Interruptor C en OFF (Bajo).

- Observación: El LED debe permanecer APAGADO. Esto confirma que el Veto está activo.

- Prueba de aprobación: Con A y B aún en ON, ponga el Interruptor C en ON.

- Observación: El LED debe encenderse (Lógica Alta, aprox. 3.5 V – 4.5 V).

- Prueba de voto único: Ponga el Interruptor A en OFF mientras B y C están en ON.

- Observación: El LED debe apagarse.

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Practical case: Veto Voting System

.width out=256

* ==============================================================================

* Components and Models

* ==============================================================================

* LED Model

.model DLED D(IS=1e-22 RS=10 N=1.5 CJO=10p)

* 74HC00 Quad 2-Input NAND Gate Subcircuit

* Pins: 1=1A, 2=1B, 3=1Y, 4=2A, 5=2B, 6=2Y, 7=GND, 8=3Y, 9=3A, 10=3B, 11=4Y, 12=4A, 13=4B, 14=VCC

.subckt 74HC00 1 2 3 4 5 6 7 8 9 10 11 12 13 14

* Logic Threshold (2.5V) and Gain (20)

.param Vth=2.5

.param K=20

* Gate 1: Inputs 1,2 -> Output 3

B1 3 7 V = V(14,7) * (1 - (1/(1+exp(-K*(V(1,7)-Vth)))) * (1/(1+exp(-K*(V(2,7)-Vth)))))

* Gate 2: Inputs 4,5 -> Output 6

B2 6 7 V = V(14,7) * (1 - (1/(1+exp(-K*(V(4,7)-Vth)))) * (1/(1+exp(-K*(V(5,7)-Vth)))))

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Practical case: Veto Voting System

.width out=256

* ==============================================================================

* Components and Models

* ==============================================================================

* LED Model

.model DLED D(IS=1e-22 RS=10 N=1.5 CJO=10p)

* 74HC00 Quad 2-Input NAND Gate Subcircuit

* Pins: 1=1A, 2=1B, 3=1Y, 4=2A, 5=2B, 6=2Y, 7=GND, 8=3Y, 9=3A, 10=3B, 11=4Y, 12=4A, 13=4B, 14=VCC

.subckt 74HC00 1 2 3 4 5 6 7 8 9 10 11 12 13 14

* Logic Threshold (2.5V) and Gain (20)

.param Vth=2.5

.param K=20

* Gate 1: Inputs 1,2 -> Output 3

B1 3 7 V = V(14,7) * (1 - (1/(1+exp(-K*(V(1,7)-Vth)))) * (1/(1+exp(-K*(V(2,7)-Vth)))))

* Gate 2: Inputs 4,5 -> Output 6

B2 6 7 V = V(14,7) * (1 - (1/(1+exp(-K*(V(4,7)-Vth)))) * (1/(1+exp(-K*(V(5,7)-Vth)))))

* Gate 3: Inputs 9,10 -> Output 8

B3 8 7 V = V(14,7) * (1 - (1/(1+exp(-K*(V(9,7)-Vth)))) * (1/(1+exp(-K*(V(10,7)-Vth)))))

* Gate 4: Inputs 12,13 -> Output 11

B4 11 7 V = V(14,7) * (1 - (1/(1+exp(-K*(V(12,7)-Vth)))) * (1/(1+exp(-K*(V(13,7)-Vth)))))

.ends 74HC00

* ==============================================================================

* Main Circuit Wiring

* ==============================================================================

* Power Supply (V1)

V1 VCC 0 DC 5

* Inputs (Simulating Switches SW1 positions A, B, C)

* Generating dynamic pulses to test the truth table (000 to 111)

* Input A (LSB, Period 100us)

Va Input_A 0 PULSE(0 5 10u 1u 1u 50u 100u)

* Input B (Period 200us)

Vb Input_B 0 PULSE(0 5 10u 1u 1u 100u 200u)

* Input C (MSB, Period 400us)

Vc Input_C 0 PULSE(0 5 10u 1u 1u 200u 400u)

* Pull-down Resistors (R1, R2, R3)

R1 Input_A 0 10k

R2 Input_B 0 10k

R3 Input_C 0 10k

* Logic IC U1 (74HC00)

* Connectivity based on Wiring Guide:

* Pin 1 (In A) -> Input_A

* Pin 2 (In B) -> Input_B

* Pin 3 (Out 1) -> Node_NAND1

* Pin 4 (In 2A) -> Node_NAND1

* Pin 5 (In 2B) -> Node_NAND1

* Pin 6 (Out 2) -> Node_AND_AB

* Pin 7 (GND) -> 0

* Pin 8 (Out 3) -> Node_NAND_FINAL

* Pin 9 (In 3A) -> Input_C

* Pin 10 (In 3B)-> Node_AND_AB

* Pin 11 (Out 4)-> Vout

* Pin 12 (In 4A)-> Node_NAND_FINAL

* Pin 13 (In 4B)-> Node_NAND_FINAL

* Pin 14 (VCC) -> VCC

XU1 Input_A Input_B Node_NAND1 Node_NAND1 Node_NAND1 Node_AND_AB 0 Node_NAND_FINAL Input_C Node_AND_AB Vout Node_NAND_FINAL Node_NAND_FINAL VCC 74HC00

* Output Stage

R4 Vout LED_Anode 330

D1 LED_Anode 0 DLED

* ==============================================================================

* Simulation Commands

* ==============================================================================

.op

.tran 1u 500u

* Print Inputs and Output to check logic (Vout should be High only when A, B, C are High)

.print tran V(Input_A) V(Input_B) V(Input_C) V(Vout)

.endResultados de Simulación (Transitorio)

Show raw data table (671 rows)

Index time v(input_a) v(input_b) v(input_c) v(vout) 0 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 1 1.000000e-08 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 2 2.000000e-08 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 3 4.000000e-08 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 4 8.000000e-08 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 5 1.600000e-07 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 6 3.200000e-07 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 7 6.400000e-07 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 8 1.280000e-06 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 9 2.280000e-06 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 10 3.280000e-06 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 11 4.280000e-06 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 12 5.280000e-06 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 13 6.280000e-06 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 14 7.280000e-06 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 15 8.280000e-06 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 16 9.280000e-06 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 17 1.000000e-05 0.000000e+00 0.000000e+00 0.000000e+00 -6.01853e-36 18 1.010000e-05 5.000000e-01 5.000000e-01 5.000000e-01 -6.01853e-36 19 1.030000e-05 1.500000e+00 1.500000e+00 1.500000e+00 -6.01853e-36 20 1.048757e-05 2.437858e+00 2.437858e+00 2.437858e+00 -6.01853e-36 21 1.071179e-05 3.558937e+00 3.558937e+00 3.558937e+00 5.000000e+00 22 1.085965e-05 4.298271e+00 4.298271e+00 4.298271e+00 5.000000e+00 23 1.099537e-05 4.976846e+00 4.976846e+00 4.976846e+00 5.000000e+00 ... (647 more rows) ...

Errores comunes y cómo evitarlos

- Entradas flotantes: Olvidar las resistencias pull-down (R1, R2, R3). Sin ellas, las entradas CMOS del 74HC00 flotarán, causando conmutación errática u oscilación.

- Confundir el pinout: El pinout del 74HC00 es estándar, pero mezclar los pines de Entrada (por ejemplo, 1 A/1B) con los pines de Salida (por ejemplo, 1Y) es común. Verifique dos veces el diagrama de la hoja de datos.

- Malinterpretar el «Veto»: En este diseño, la Entrada C es una línea de «Habilitación» (Activa Alta). Si piensa en el Veto como «Interruptor ON para Bloquear» (lógica Activa Baja), el cableado del Interruptor C necesitaría ser invertido. Aquí, Interruptor C ON significa «Autorizar».

Solución de problemas

- El LED nunca se enciende: Compruebe que la polaridad del LED sea correcta (Ánodo a la resistencia, Cátodo a GND). Verifique que U1 esté alimentado (Pin 14 a 5 V, Pin 7 a GND).

- El LED permanece encendido incluso cuando los interruptores están en OFF: Compruebe si faltan o están desconectadas R1, R2 o R3. Asegúrese de no estar utilizando interruptores NC (Normalmente Cerrados) por error.

- El circuito funciona para A y B pero C no tiene efecto: Compruebe el cableado en la Puerta 3 (Pines 8, 9, 10). Asegúrese de que el pin 9 se conecte al Interruptor C y el pin 10 se conecte a la salida de la etapa anterior (Pin 6).

Posibles mejoras y extensiones

- Indicador de veto: Añada un segundo LED (Verde) controlado por una puerta no utilizada (o un transistor) conectado a la Entrada C, indicando «Sesión Abierta» (Autorización Concedida) o «Sesión Bloqueada» (Veto).

- Modificación de voto por mayoría: Rediseñe el circuito para permitir que la propuesta se apruebe si cualesquiera dos de los tres miembros (A, B, C) votan Sí, eliminando el poder de veto específico y haciendo que todos los miembros sean iguales.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.