Nivel: Avanzado — Diseñar un circuito para aprobar una moción si al menos uno de tres jueces emite un voto positivo, integrando lógica combinacional y eliminación de rebotes (debouncing).

Objetivo y caso de uso

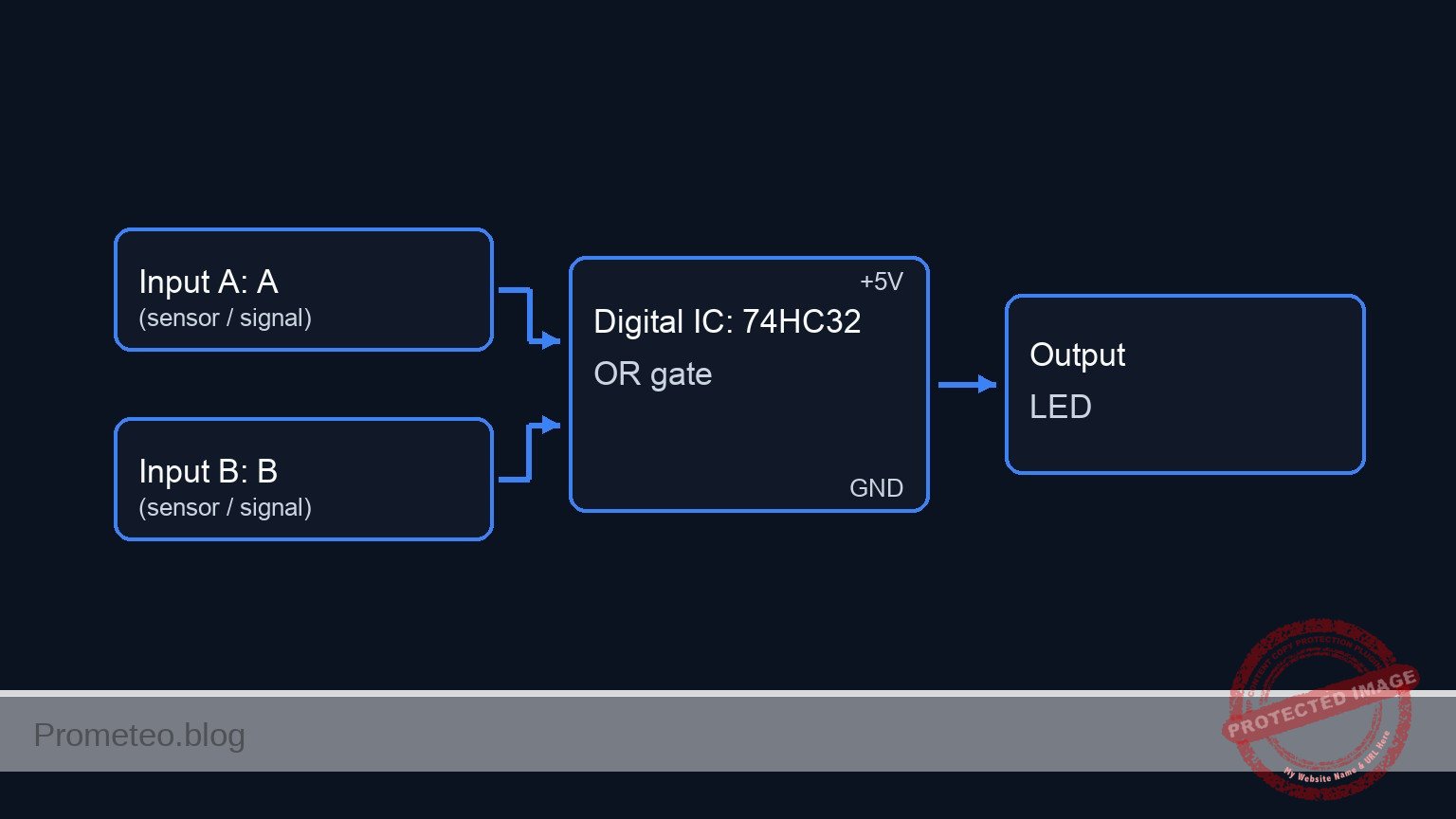

Construirás un circuito lógico digital que procesa señales de tres interruptores momentáneos independientes que representan a los jueces. El sistema utiliza una topología OR en cascada para activar un indicador visual si cualquier entrada individual (o combinación de entradas) está activa.

Por qué es útil:

* Enclavamientos de seguridad: Se utiliza una lógica similar en protecciones de máquinas donde romper cualquier haz de luz o abrir cualquier puerta debe activar una parada o alarma.

* Detección de fallos: En los tableros de instrumentos de automóviles, múltiples sensores (aceite, presión de neumáticos, calor del motor) alimentan una luz de advertencia central (Check Engine) a través de lógica OR.

* Control de acceso: Sistemas donde múltiples credenciales diferentes (tarjeta, código o biométrico) pueden otorgar entrada a la misma puerta.

* Solicitudes de interrupción: En microcontroladores, múltiples periféricos pueden activar una sola línea de interrupción a la CPU utilizando esta lógica.

Resultado esperado:

* El LED de salida se ENCIENDE (Lógica Alta) si el Juez A, el Juez B, el Juez C, o cualquier combinación presiona su botón.

* El LED de salida permanece APAGADO (Lógica Baja) solo cuando todos los botones están liberados.

* Las señales de entrada son acondicionadas (anti-rebote) para evitar el parpadeo rápido causado por el rebote mecánico del interruptor.

* Verificación de la propagación de la señal a través de puertas lógicas en cascada.

Público objetivo: Estudiantes de ingeniería y entusiastas avanzados de la electrónica.

Materiales

- V1: Fuente de alimentación de 5 V CC

- S1: Pulsador momentáneo (Normalmente Abierto), función: Entrada Juez A

- S2: Pulsador momentáneo (Normalmente Abierto), función: Entrada Juez B

- S3: Pulsador momentáneo (Normalmente Abierto), función: Entrada Juez C

- R1: Resistencia de 10 kΩ, función: pull-down para el Nodo A

- R2: Resistencia de 10 kΩ, función: pull-down para el Nodo B

- R3: Resistencia de 10 kΩ, función: pull-down para el Nodo C

- R4: Resistencia de 1 kΩ, función: resistencia serie para anti-rebote RC (Entrada A)

- R5: Resistencia de 1 kΩ, función: resistencia serie para anti-rebote RC (Entrada B)

- R6: Resistencia de 1 kΩ, función: resistencia serie para anti-rebote RC (Entrada C)

- C1: Condensador de 100 nF, función: filtrado de rebotes (Entrada A)

- C2: Condensador de 100 nF, función: filtrado de rebotes (Entrada B)

- C3: Condensador de 100 nF, función: filtrado de rebotes (Entrada C)

- U1: 74HC32 (CI de 4 puertas OR de 2 entradas)

- R7: Resistencia de 330 Ω, función: limitación de corriente del LED

- D1: LED rojo, función: indicador de resultado

Pin-out del CI utilizado

Chip seleccionado: 74HC32 (Cuádruple puerta OR de 2 entradas).

Nota: Dado que tenemos 3 entradas y el chip contiene puertas de 2 entradas, conectaremos en cascada dos puertas para crear la función lógica $Y = (A + B) + C$.

| Pin | Nombre | Función lógica | Conexión en este caso |

|---|---|---|---|

| 1 | 1A | Entrada | Conecta a Señal A con anti-rebote |

| 2 | 1B | Entrada | Conecta a Señal B con anti-rebote |

| 3 | 1Y | Salida | Conecta al Pin 4 (Cascada a la siguiente puerta) |

| 4 | 2A | Entrada | Conecta al Pin 3 (Resultado de A+B) |

| 5 | 2B | Entrada | Conecta a Señal C con anti-rebote |

| 6 | 2Y | Salida | Conecta al circuito del LED de salida |

| 7 | GND | Tierra | Conecta a 0 (GND) |

| 14 | VCC | Alimentación | Conecta a VCC (+5V) |

Guía de conexionado

Esta guía utiliza nombres de nodos compatibles con SPICE.

* Fuente de alimentación:

* V1 conecta entre el nodo VCC y el nodo 0 (GND).

* U1 pin 14 conecta a VCC.

* U1 pin 7 conecta a 0.

- Etapa de entrada (Juez A) – Pull-down y Anti-rebote:

- S1 conecta entre

VCCy el nodoRAW_A. - R1 conecta entre

RAW_Ay0. - R4 conecta entre

RAW_Ay el nodoIN_A. -

C1 conecta entre

IN_Ay0. -

Etapa de entrada (Juez B) – Pull-down y Anti-rebote:

- S2 conecta entre

VCCy el nodoRAW_B. - R2 conecta entre

RAW_By0. - R5 conecta entre

RAW_By el nodoIN_B. -

C2 conecta entre

IN_By0. -

Etapa de entrada (Juez C) – Pull-down y Anti-rebote:

- S3 conecta entre

VCCy el nodoRAW_C. - R3 conecta entre

RAW_Cy0. - R6 conecta entre

RAW_Cy el nodoIN_C. -

C3 conecta entre

IN_Cy0. -

Procesamiento lógico (OR en cascada):

- U1 pin 1 conecta a

IN_A. - U1 pin 2 conecta a

IN_B. - U1 pin 3 (Salida Puerta 1) conecta al nodo

GATE1_OUT. - U1 pin 4 conecta al nodo

GATE1_OUT(Señal en cascada). - U1 pin 5 conecta a

IN_C. -

U1 pin 6 (Salida Final) conecta al nodo

LOGIC_OUT. -

Etapa de salida:

- R7 conecta entre

LOGIC_OUTy el nodoLED_ANODE. - D1 conecta entre

LED_ANODE(Ánodo) y0(Cátodo).

Diagrama de bloques conceptual

Esquemático

[ INPUT / CONDITIONING ] [ LOGIC PROCESSING (74HC32) ] [ OUTPUT ]

+-------------------------+

[ S1: Judge A ] | U1: Gate 1 |

(VCC -> RAW_A) -> [ R1/R4/C1 ] --(Pin 1)--->| Input A |

(Debounce) | OR |

| Input B (Output) |

[ S2: Judge B ] +------->| Pin 2 Pin 3 |--+

(VCC -> RAW_B) -> [ R2/R5/C2 ] ----+ +-------------------------+ |

(Debounce) |

|

|

+-------------------------+ |

| U1: Gate 2 | |

| (Cascade In) Pin 4 |< +

| OR |

[ S3: Judge C ] +------->| Input C (Output) |

(VCC -> RAW_C) -> [ R3/R6/C3 ] ----+ | Pin 5 Pin 6 |-----> [ R7: 330 Ohm ]

(Debounce) +-------------------------+ |

v

[ D1: Red LED ]

|

v

GND

Tabla de verdad

El sistema crea una función OR de 3 entradas: $Q = A + B + C$.

| Entrada A | Entrada B | Entrada C | Salida Q (LED) | Nota |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | Moción rechazada |

| 0 | 0 | 1 | 1 | Moción aprobada |

| 0 | 1 | 0 | 1 | Moción aprobada |

| 0 | 1 | 1 | 1 | Moción aprobada |

| 1 | 0 | 0 | 1 | Moción aprobada |

| 1 | 0 | 1 | 1 | Moción aprobada |

| 1 | 1 | 0 | 1 | Moción aprobada |

| 1 | 1 | 1 | 1 | Moción aprobada |

Mediciones y pruebas

- Comprobación lógica estática: Asegúrate de que no haya botones presionados. Mide el voltaje en el Pin 6 de U1. Debería estar cerca de 0 V. Presiona S1. El voltaje debería subir a ~5 V. Repite para S2 y S3 individualmente.

- Validación de anti-rebote: Conecta un osciloscopio a

RAW_AyIN_A. Presiona S1.RAW_Apuede mostrar picos de voltaje agudos/ruido al contacto.IN_Adebería mostrar una curva de ascenso exponencial suave, filtrando el ruido antes de que llegue a la puerta lógica. - Retardo en cascada: Esta es una medición avanzada. Mide el retardo de propagación entre

IN_AyLOGIC_OUTfrente aIN_CyLOGIC_OUT. Debido a queIN_Adebe pasar por dos puertas (Puerta 1 y luego Puerta 2), el retardo de propagación total será ligeramente mayor queIN_C, que solo pasa por la Puerta 2.

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Simple electronic voting system

* Based on Practical Case BOM and Wiring Guide

* --- Power Supply ---

* V1 connects between node VCC and node 0 (GND).

V1 VCC 0 DC 5

* --- User Input Stimuli (Button Presses) ---

* We simulate the physical push-buttons using Voltage Controlled Switches (S1-S3)

* controlled by independent PULSE sources (V_CTRL_A, etc.) to mimic user behavior.

* The timing is staggered to test inputs A, B, and C sequentially with sufficient

* time for the RC debounce circuits to charge and discharge.

* Judge A: Press at 1ms, hold for 2ms (releases at 3ms)

V_CTRL_A CTRL_A 0 PULSE(0 5 1m 1u 1u 2m 20m)

* Judge B: Press at 6ms, hold for 2ms (releases at 8ms)

V_CTRL_B CTRL_B 0 PULSE(0 5 6m 1u 1u 2m 20m)

* Judge C: Press at 11ms, hold for 2ms (releases at 13ms)

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Simple electronic voting system

* Based on Practical Case BOM and Wiring Guide

* --- Power Supply ---

* V1 connects between node VCC and node 0 (GND).

V1 VCC 0 DC 5

* --- User Input Stimuli (Button Presses) ---

* We simulate the physical push-buttons using Voltage Controlled Switches (S1-S3)

* controlled by independent PULSE sources (V_CTRL_A, etc.) to mimic user behavior.

* The timing is staggered to test inputs A, B, and C sequentially with sufficient

* time for the RC debounce circuits to charge and discharge.

* Judge A: Press at 1ms, hold for 2ms (releases at 3ms)

V_CTRL_A CTRL_A 0 PULSE(0 5 1m 1u 1u 2m 20m)

* Judge B: Press at 6ms, hold for 2ms (releases at 8ms)

V_CTRL_B CTRL_B 0 PULSE(0 5 6m 1u 1u 2m 20m)

* Judge C: Press at 11ms, hold for 2ms (releases at 13ms)

V_CTRL_C CTRL_C 0 PULSE(0 5 11m 1u 1u 2m 20m)

* --- Input Stage: Judge A ---

* S1 connects between VCC and node RAW_A

S1 VCC RAW_A CTRL_A 0 SW_PB

* R1 (10k) pull-down for Node A (RAW_A to 0)

R1 RAW_A 0 10k

* R4 (1k) RC debounce series resistance (RAW_A to IN_A)

R4 RAW_A IN_A 1k

* C1 (100nF) debounce filtering (IN_A to 0)

C1 IN_A 0 100n

* --- Input Stage: Judge B ---

* S2 connects between VCC and node RAW_B

S2 VCC RAW_B CTRL_B 0 SW_PB

* R2 (10k) pull-down for Node B (RAW_B to 0)

R2 RAW_B 0 10k

* R5 (1k) RC debounce series resistance (RAW_B to IN_B)

R5 RAW_B IN_B 1k

* C2 (100nF) debounce filtering (IN_B to 0)

C2 IN_B 0 100n

* --- Input Stage: Judge C ---

* S3 connects between VCC and node RAW_C

S3 VCC RAW_C CTRL_C 0 SW_PB

* R3 (10k) pull-down for Node C (RAW_C to 0)

R3 RAW_C 0 10k

* R6 (1k) RC debounce series resistance (RAW_C to IN_C)

R6 RAW_C IN_C 1k

* C3 (100nF) debounce filtering (IN_C to 0)

C3 IN_C 0 100n

* --- Logic Processing: U1 (74HC32 Quad 2-Input OR Gate) ---

* Implemented using Behavioral Voltage Sources (B-sources) for robust simulation.

* Logic Transfer Function: Continuous Sigmoid approximation of OR gate.

* Vout = VCC * Sigmoid( max(Input1, Input2) - Threshold )

* Threshold set to 2.5V (Mid-rail).

* U1 Pin 14 (VCC) and Pin 7 (GND) are functionally represented by the V(VCC) term and node 0 reference.

* Gate 1: Inputs IN_A (Pin 1), IN_B (Pin 2) -> Output GATE1_OUT (Pin 3)

* Corresponds to wiring: U1 pin 1 to IN_A, U1 pin 2 to IN_B, U1 pin 3 to GATE1_OUT

B_U1_G1 GATE1_OUT 0 V = V(VCC) * (1 / (1 + exp(-20 * (max(V(IN_A), V(IN_B)) - 2.5))))

* Cascading Connection:

* Wiring: U1 pin 4 connects to node GATE1_OUT.

* Gate 2: Inputs GATE1_OUT (Pin 4), IN_C (Pin 5) -> Output LOGIC_OUT (Pin 6)

* Corresponds to wiring: U1 pin 4 to GATE1_OUT, U1 pin 5 to IN_C, U1 pin 6 to LOGIC_OUT

B_U1_G2 LOGIC_OUT 0 V = V(VCC) * (1 / (1 + exp(-20 * (max(V(GATE1_OUT), V(IN_C)) - 2.5))))

* --- Output Stage ---

* R7 connects between LOGIC_OUT and node LED_ANODE

R7 LOGIC_OUT LED_ANODE 330

* D1 connects between LED_ANODE (Anode) and 0 (Cathode)

D1 LED_ANODE 0 D_LED

* --- Models ---

* Switch model for push buttons (Active High control)

.model SW_PB SW(Vt=2.5 Ron=0.1 Roff=10Meg)

* Generic LED model (Red)

.model D_LED D(IS=1n N=2 RS=10 BV=5)

* --- Simulation Directives ---

* Transient analysis for 15ms to capture all button presses and RC discharge curves.

* Step size 10us is sufficient for the 100us/1.1ms time constants.

.tran 10u 15m

* Print required nodes for validation

.print tran V(IN_A) V(IN_B) V(IN_C) V(GATE1_OUT) V(LOGIC_OUT) V(LED_ANODE)

.op

.endResultados de Simulación (Transitorio)

Show raw data table (3274 rows)

Index time v(in_a) v(in_b) v(in_c) 0 0.000000e+00 4.995005e-03 4.995005e-03 4.995005e-03 1 1.000000e-07 4.995005e-03 4.995005e-03 4.995005e-03 2 2.000000e-07 4.995005e-03 4.995005e-03 4.995005e-03 3 4.000000e-07 4.995005e-03 4.995005e-03 4.995005e-03 4 8.000000e-07 4.995005e-03 4.995005e-03 4.995005e-03 5 1.600000e-06 4.995005e-03 4.995005e-03 4.995005e-03 6 3.200000e-06 4.995005e-03 4.995005e-03 4.995005e-03 7 6.400000e-06 4.995005e-03 4.995005e-03 4.995005e-03 8 1.280000e-05 4.995005e-03 4.995005e-03 4.995005e-03 9 2.280000e-05 4.995005e-03 4.995005e-03 4.995005e-03 10 3.280000e-05 4.995005e-03 4.995005e-03 4.995005e-03 11 4.280000e-05 4.995005e-03 4.995005e-03 4.995005e-03 12 5.280000e-05 4.995005e-03 4.995005e-03 4.995005e-03 13 6.280000e-05 4.995005e-03 4.995005e-03 4.995005e-03 14 7.280000e-05 4.995005e-03 4.995005e-03 4.995005e-03 15 8.280000e-05 4.995005e-03 4.995005e-03 4.995005e-03 16 9.280000e-05 4.995005e-03 4.995005e-03 4.995005e-03 17 1.028000e-04 4.995005e-03 4.995005e-03 4.995005e-03 18 1.128000e-04 4.995005e-03 4.995005e-03 4.995005e-03 19 1.228000e-04 4.995005e-03 4.995005e-03 4.995005e-03 20 1.328000e-04 4.995005e-03 4.995005e-03 4.995005e-03 21 1.428000e-04 4.995005e-03 4.995005e-03 4.995005e-03 22 1.528000e-04 4.995005e-03 4.995005e-03 4.995005e-03 23 1.628000e-04 4.995005e-03 4.995005e-03 4.995005e-03 ... (3250 more rows) ...

Errores comunes y cómo evitarlos

- Entradas flotantes: No instalar las resistencias pull-down (R1, R2, R3). Sin ellas, las entradas del 74HC32 actúan como antenas, haciendo que el LED parpadee aleatoriamente o se quede atascado en Alto. Solución: Siempre referencia las entradas a GND cuando el interruptor esté abierto.

- Ignorar el pinout: Conectar la Entrada C al Pin 3 (que es una salida). Esto crea un cortocircuito cuando la puerta intenta conducir a Bajo mientras el botón conduce a Alto. Solución: Comprueba dos veces el diagrama de pines en la hoja de datos antes de encender.

- Constante de tiempo RC excesiva: Usar un condensador demasiado grande (por ejemplo, 100 µF) para el circuito de anti-rebote. Esto crea un aumento de voltaje muy lento que hace que la puerta digital oscile linealmente durante el cruce del umbral. Solución: Cíñete a 100 nF – 1 µF para entradas lógicas simples.

Solución de problemas

- El LED está siempre ENCENDIDO: Comprueba las resistencias pull-down. Si el voltaje medido en los pines 1, 2 o 5 es flotante (no 0 V), la puerta lo interpreta como Lógica Alta.

- El LED no se enciende para el Juez A o B: Verifica la conexión en cascada. El Pin 3 (Salida de la primera puerta) debe estar físicamente cableado al Pin 4 (Entrada de la segunda puerta).

- Comportamiento errático al tocar los cables: Indica falta de conexiones a tierra en entradas no utilizadas (si las hay) o entradas operativas flotantes. Asegúrate de que todas las tierras compartan un punto común.

- La puerta se calienta: Comprueba si hay cortocircuitos de salida a salida o de salida a VCC. Desconecta la alimentación inmediatamente.

Posibles mejoras y extensiones

- Extensión de voto por mayoría: Modificar la lógica para requerir al menos dos votos positivos para aprobar la moción (utilizando una combinación de puertas AND y OR: $AB + BC + AC$).

- Funcionalidad de cerrojo (Latch): Añadir un Flip-Flop D (por ejemplo, 74HC74) después de la salida. Una vez aprobada la moción (LED ENCENDIDO), la luz permanece ENCENDIDA hasta que un supervisor presione un botón dedicado de «Reset».

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.