Nivel: Medio – Implementar un sistema de autenticación de doble interruptor para activar un mecanismo de cerradura electrónica.

Objetivo y caso de uso

En este proyecto, construirá un circuito de seguridad basado en hardware que controla una cerradura electrónica (solenoide) utilizando una compuerta AND 74HC08. El sistema valida que dos señales de autorización distintas estén presentes simultáneamente antes de conceder el acceso.

Por qué es útil:

* Enclavamientos de seguridad: Imita los controles de maquinaria industrial que requieren operación a dos manos para prevenir lesiones.

* Acceso de seguridad: Simula una «Autenticación de dos factores» (2FA) simplificada donde una llave y un código deben estar activos al mismo tiempo.

* Control lógico: Demuestra cómo interconectar compuertas lógicas de baja potencia con actuadores electromecánicos de alta potencia.

Resultado esperado:

* El Solenoide se activa (desbloquea) SOLO cuando tanto el Interruptor A COMO el Interruptor B están en estado ALTO (lógica 1).

* El LED indicador se enciende simultáneamente con la activación del solenoide.

* Salida lógica: Mide ~5V en la salida de la compuerta durante la activación y ~0V en caso contrario.

* Público objetivo: Estudiantes de electrónica de nivel intermedio familiarizados con la lógica digital básica.

Materiales

- V1: Fuente de alimentación de 5 V CC, función: Alimentación del circuito principal.

- U1: 74HC08, función: CI de cuatro compuertas AND de 2 entradas.

- S1: Interruptor DIP (SPST), función: Entrada A (Llave de seguridad 1).

- S2: Interruptor DIP (SPST), función: Entrada B (Llave de seguridad 2).

- R1: Resistencia de 10 kΩ, función: Pull-down para la Entrada A.

- R2: Resistencia de 10 kΩ, función: Pull-down para la Entrada B.

- R3: Resistencia de 1 kΩ, función: Limitación de corriente de base del transistor.

- R4: Resistencia de 330 Ω, función: Limitación de corriente del LED.

- Q1: 2N2222 (BJT NPN), función: Interruptor controlador (driver) para el solenoide.

- D1: Diodo 1N4007, función: Protección Flyback/Snubber para el transistor.

- D2: LED verde, función: Indicador visual de estado.

- L1: Solenoide de 5 V / 100 mA (representado como Inductor+Resistencia), función: Mecanismo de cerradura electrónica.

Pin-out del 74HC08

Chip seleccionado: 74HC08 (Cuatro compuertas AND de 2 entradas)

| Pin | Nombre | Función lógica | Conexión en este caso |

|---|---|---|---|

| 1 | 1A | Entrada A | Conectado al Nodo VA (Interruptor S1) |

| 2 | 1B | Entrada B | Conectado al Nodo VB (Interruptor S2) |

| 3 | 1Y | Salida | Conectado al Nodo V_GATE |

| 7 | GND | Tierra | Conectado al Nodo 0 |

| 14 | VCC | Fuente de alimentación | Conectado al Nodo VCC (+5V) |

Guía de conexionado

Construya el circuito siguiendo estas conexiones de nodos explícitas:

- Riel de alimentación:

- Conecte el terminal positivo de V1 al nodo VCC.

- Conecte el terminal negativo de V1 al nodo 0 (GND).

-

Conecte el pin 14 de U1 a VCC y el pin 7 a 0.

-

Etapa de entrada (Sensores):

- Conecte S1 entre VCC y el nodo VA.

- Conecte R1 entre VA y 0.

- Conecte el pin 1 de U1 (Entrada 1A) al nodo VA.

- Conecte S2 entre VCC y el nodo VB.

- Conecte R2 entre VB y 0.

-

Conecte el pin 2 de U1 (Entrada 1B) al nodo VB.

-

Etapa lógica:

-

El pin 3 de U1 (Salida 1Y) define el nodo V_GATE.

-

Etapa de salida (Controlador del actuador):

- Conecte R3 entre V_GATE y la Base de Q1.

- Conecte el Emisor de Q1 directamente a 0.

- Conecte el Colector de Q1 al nodo V_LOCK.

- Conecte L1 (Solenoide) entre VCC y V_LOCK.

-

Conecte D1 (Cátodo a VCC, Ánodo a V_LOCK) en paralelo con el solenoide para proteger Q1.

-

Etapa indicadora:

- Conecte R4 entre V_LOCK y el Ánodo de D2.

- ¿Conecte el Cátodo de D2 al nodo 0? Corrección: Dado que Q1 conmuta el lado bajo, conecte R4 + D2 en paralelo con el solenoide para ver cuándo está energizado, o simplemente conecte R4 desde V_GATE al Ánodo de D2, y el Cátodo de D2 a 0 para visualizar la señal lógica. Usemos esto último para una visualización lógica más clara: Conecte R4 entre V_GATE y el Ánodo de D2; Cátodo de D2 a 0.

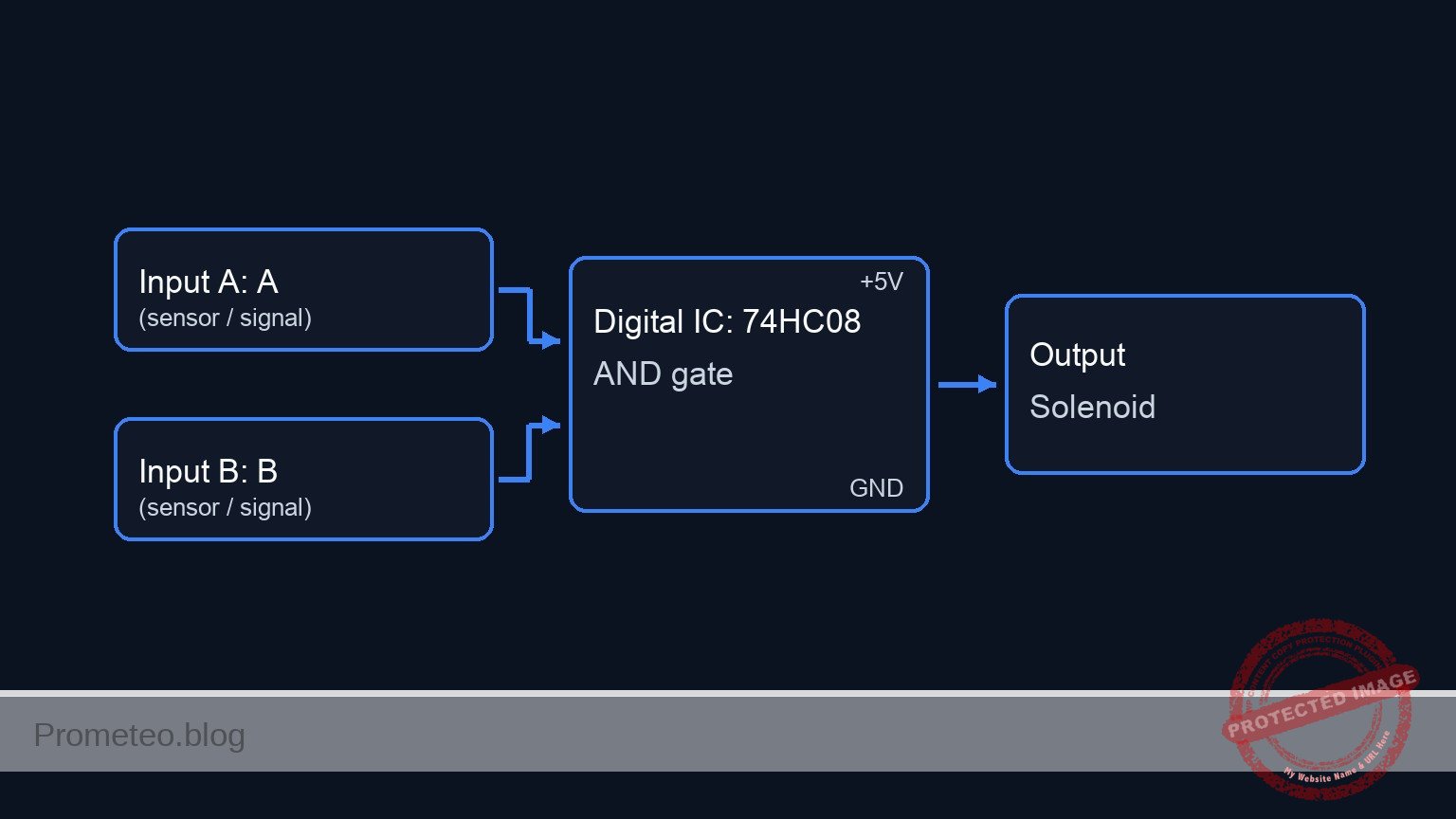

Diagrama de bloques conceptual

Esquemático

[ INPUT SENSORS ] [ LOGIC PROCESSING ] [ OUTPUT ACTUATORS ]

(Visual Status)

[ Switch S1 ] +----------------+ +---> [ Resistor R4 ] --> [ LED D2 ] --> GND

(w/ R1 Pull-down) --(Node VA)->| Pin 1 | |

| | |

| U1: 74HC08 |--(V_GATE)+

| (AND Gate) | (Pin 3) |

| | |

[ Switch S2 ] | Pin 2 | | (Solenoid Driver)

(w/ R2 Pull-down) --(Node VB)->| | +---> [ Resistor R3 ] --> [ Transistor Q1 ]

+----------------+ |

(Collector)

|

V

[ Solenoid L1 + Diode D1 ]

(Connected to VCC)

Tabla de verdad

Esta tabla describe el estado lógico de la salida del 74HC08 y el estado físico del solenoide.

| Entrada A (S1) | Entrada B (S2) | Salida Y (V_GATE) | Estado del solenoide |

|---|---|---|---|

| 0 (Bajo) | 0 (Bajo) | 0 (Bajo) | Bloqueado (OFF) |

| 0 (Bajo) | 1 (Alto) | 0 (Bajo) | Bloqueado (OFF) |

| 1 (Alto) | 0 (Bajo) | 0 (Bajo) | Bloqueado (OFF) |

| 1 (Alto) | 1 (Alto) | 1 (Alto) | Desbloqueado (ON) |

Mediciones y pruebas

- Comprobación en reposo: Con ambos interruptores OFF, mida el voltaje en V_GATE. Debería ser cercano a 0 V. El solenoide debe estar relajado.

- Activación parcial: Encienda solo S1. Mida el voltaje en VA (debe ser 5 V) y VB (debe ser 0 V). Asegúrese de que V_GATE permanezca en 0 V.

- Activación completa: Encienda tanto S1 como S2.

- Mida V_GATE: Debe leer ~5 V (Lógica Alta).

- Observe L1: El solenoide debe retraerse/hacer clic.

- Mida el voltaje en V_LOCK: Debe caer cerca de 0 V (voltaje de saturación de Q1), permitiendo que la corriente fluya desde VCC a través del solenoide.

- Consumo de corriente: Mida la corriente que sale de V1. Debe aumentar significativamente (p. ej., +100mA dependiendo del solenoide) solo cuando ambas entradas sean Altas.

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Simple security code validation

* ==============================================================================

* POWER SUPPLY

* ==============================================================================

V1 VCC 0 DC 5

* ==============================================================================

* INPUT STAGE (Switches & Pull-downs)

* ==============================================================================

* Note: S1 and S2 are simulated using Pulse Voltage Sources to generate

* dynamic logic patterns for validation.

* R1 and R2 are included as physical pull-down resistors per BOM.

* Input A (S1)

* Generates a pulse: Low for 0.5ms, High for 1ms, Period 2ms

V_S1 VA 0 PULSE(0 5 0.5m 1u 1u 1m 2m)

R1 VA 0 10k

* Input B (S2)

* Generates a pulse: High for 2ms, Low for 2ms, Period 4ms

V_S2 VB 0 PULSE(0 5 0 1u 1u 2m 4m)

R2 VB 0 10k

* ==============================================================================

* LOGIC STAGE (U1: 74HC08 Quad AND Gate)

* ==============================================================================

* Subcircuit to model one gate of the 74HC08, exposing power pins.

* Uses continuous behavioral modeling (sigmoid) for convergence.

.subckt 74HC08_GATE IN1 IN2 OUT VCC_PIN GND_PIN

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Simple security code validation

* ==============================================================================

* POWER SUPPLY

* ==============================================================================

V1 VCC 0 DC 5

* ==============================================================================

* INPUT STAGE (Switches & Pull-downs)

* ==============================================================================

* Note: S1 and S2 are simulated using Pulse Voltage Sources to generate

* dynamic logic patterns for validation.

* R1 and R2 are included as physical pull-down resistors per BOM.

* Input A (S1)

* Generates a pulse: Low for 0.5ms, High for 1ms, Period 2ms

V_S1 VA 0 PULSE(0 5 0.5m 1u 1u 1m 2m)

R1 VA 0 10k

* Input B (S2)

* Generates a pulse: High for 2ms, Low for 2ms, Period 4ms

V_S2 VB 0 PULSE(0 5 0 1u 1u 2m 4m)

R2 VB 0 10k

* ==============================================================================

* LOGIC STAGE (U1: 74HC08 Quad AND Gate)

* ==============================================================================

* Subcircuit to model one gate of the 74HC08, exposing power pins.

* Uses continuous behavioral modeling (sigmoid) for convergence.

.subckt 74HC08_GATE IN1 IN2 OUT VCC_PIN GND_PIN

B_AND OUT GND_PIN V = V(VCC_PIN) * (1 / (1 + exp(-20*(V(IN1)-2.5)))) * (1 / (1 + exp(-20*(V(IN2)-2.5))))

.ends

* Instantiate U1 (only one gate used: Inputs 1A, 1B -> Output 1Y)

* Pin 1=VA, Pin 2=VB, Pin 3=V_GATE, Pin 14=VCC, Pin 7=0 (GND)

XU1 VA VB V_GATE VCC 0 74HC08_GATE

* ==============================================================================

* INDICATOR STAGE

* ==============================================================================

* R4 limits current to LED D2

R4 V_GATE LED_A 330

D2 LED_A 0 LED_GREEN

* ==============================================================================

* OUTPUT STAGE (Actuator Driver)

* ==============================================================================

* Base resistor

R3 V_GATE Q1_B 1k

* Transistor Q1 (2N2222)

* Collector -> V_LOCK, Base -> Q1_B, Emitter -> 0

Q1 V_LOCK Q1_B 0 2N2222

* Solenoid L1 (Modeled as Inductor + Series Resistor)

* 5V / 100mA = 50 Ohm DC resistance. Inductance approx 10mH.

* Connected between VCC and V_LOCK.

R_L1 VCC INT_SOL 50

L1 INT_SOL V_LOCK 10mH

* Flyback Diode D1

* Cathode to VCC, Anode to V_LOCK

D1 V_LOCK VCC 1N4007

* ==============================================================================

* MODELS

* ==============================================================================

.model 2N2222 NPN (IS=1E-14 BF=200 VAF=100 CJC=8p CJE=25p TR=400n TF=1n)

.model 1N4007 D (IS=1N RS=0.1 BV=1000 IBV=10u N=1.7)

.model LED_GREEN D (IS=1e-22 RS=5 N=1.5 BV=5 IBV=10u CJO=10p)

* ==============================================================================

* SIMULATION COMMANDS

* ==============================================================================

.op

.tran 10u 5m

* Print logic states and output voltage

.print tran V(VA) V(VB) V(V_GATE) V(V_LOCK)

.endResultados de Simulación (Transitorio)

Show raw data table (4960 rows)

Index time v(va) v(vb) v(v_gate) 0 0.000000e+00 0.000000e+00 0.000000e+00 1.860038e-43 1 1.000000e-08 0.000000e+00 5.000000e-02 3.720076e-43 2 2.000000e-08 0.000000e+00 1.000000e-01 1.011221e-42 3 4.000000e-08 0.000000e+00 2.000000e-01 4.123178e-42 4 8.000000e-08 0.000000e+00 4.000000e-01 5.077732e-41 5 1.600000e-07 0.000000e+00 8.000000e-01 4.990226e-39 6 3.200000e-07 0.000000e+00 1.600000e+00 2.809846e-35 7 6.400000e-07 0.000000e+00 3.200000e+00 4.846845e-28 8 1.000000e-06 0.000000e+00 5.000000e+00 9.644030e-22 9 1.064000e-06 0.000000e+00 5.000000e+00 9.643749e-22 10 1.192000e-06 0.000000e+00 5.000000e+00 9.643749e-22 11 1.448000e-06 0.000000e+00 5.000000e+00 9.643749e-22 12 1.960000e-06 0.000000e+00 5.000000e+00 9.643749e-22 13 2.984000e-06 0.000000e+00 5.000000e+00 9.643749e-22 14 5.032000e-06 0.000000e+00 5.000000e+00 9.643749e-22 15 9.128000e-06 0.000000e+00 5.000000e+00 9.643749e-22 16 1.732000e-05 0.000000e+00 5.000000e+00 9.643749e-22 17 2.732000e-05 0.000000e+00 5.000000e+00 9.643749e-22 18 3.732000e-05 0.000000e+00 5.000000e+00 9.643749e-22 19 4.732000e-05 0.000000e+00 5.000000e+00 9.643749e-22 20 5.732000e-05 0.000000e+00 5.000000e+00 9.643749e-22 21 6.732000e-05 0.000000e+00 5.000000e+00 9.643749e-22 22 7.732000e-05 0.000000e+00 5.000000e+00 9.643749e-22 23 8.732000e-05 0.000000e+00 5.000000e+00 9.643749e-22 ... (4936 more rows) ...

Errores comunes y cómo evitarlos

- Entradas flotantes: Olvidar las resistencias R1 o R2 hace que las entradas «floten», lo que lleva a un disparo errático de la cerradura causado por la electricidad estática. Utilice siempre resistencias pull-down con lógica CMOS como la serie 74HC.

- Conducir el solenoide directamente: Conectar el solenoide directamente al pin de salida del 74HC08 (pin 3). El chip solo puede suministrar ~20mA, mientras que un solenoide necesita >100mA. Esto destruirá el chip. Utilice siempre un transistor controlador (Q1).

- Omitir el diodo Flyback: Olvidar D1 a través del solenoide. Cuando el solenoide se apaga, genera un pico de alto voltaje (fuerza contraelectromotriz) que destruye el transistor instantáneamente.

Solución de problemas

- El solenoide no se activa pero el LED funciona: La lógica es correcta, pero la capacidad de conducción es insuficiente. Verifique las conexiones de Q1 y asegúrese de que el requerimiento de potencia del solenoide coincida con la fuente.

- La compuerta lógica se calienta: Es posible que haya cortocircuitado el pin de salida a tierra o esté intentando conducir el solenoide directamente. Desconecte inmediatamente y verifique el cableado del pin 3.

- El circuito funciona inversamente (se desbloquea cuando los interruptores están OFF): Es posible que haya conectado las resistencias pull-down como pull-ups o conectado el transistor al riel incorrecto. Verifique que R1 y R2 vayan a Tierra.

- La Entrada A activa la cerradura sin la Entrada B: Verifique si hay un cortocircuito entre el pin 1 y el pin 2, o verifique si el pin 2 está conectado accidentalmente a VCC.

Posibles mejoras y extensiones

- Agregar un temporizador: Alimente la salida del 74HC08 a un temporizador 555 (modo monoestable) para que la cerradura permanezca abierta durante 5 segundos incluso si el usuario suelta los interruptores inmediatamente.

- Ampliar la seguridad: Conecte en cascada un segundo 74HC08 para agregar un tercer interruptor (Interruptor A AND Interruptor B AND Interruptor C) para una mayor seguridad.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.