Nivel: Básico. Verifique el funcionamiento de un contador binario de 4 bits visualizando la secuencia de conteo con LEDs.

Objetivo y caso de uso

En este caso práctico, construirá un circuito digital síncrono utilizando el circuito integrado 74HC161 para contar pulsos de reloj en binario desde 0 (0000) hasta 15 (1111). Visualizará los estados de salida utilizando cuatro LEDs que representan los bits desde LSB (Bit menos significativo) hasta MSB (Bit más significativo).

Por qué es útil:

* Relojes digitales: Forma el bloque fundamental para el seguimiento del tiempo (segundos, minutos, horas).

* División de frecuencia: Los contadores se utilizan para reducir señales de reloj de alta frecuencia a frecuencias más bajas y utilizables para otros componentes.

* Direccionamiento de memoria: En sistemas informáticos, los contadores generan direcciones secuenciales para acceder a datos en la memoria.

* Conteo de eventos: Útil en automatización industrial para contar artículos en una cinta transportadora o activaciones de sensores.

* Máquinas de estados: Proporciona la secuencia de estados requerida para controlar operaciones lógicas digitales complejas.

Resultado esperado:

* Cuatro LEDs (D1–D4) se encenderán en un patrón binario (0000, 0001, 0010… 1111).

* La secuencia se repite cada 16 pulsos de reloj.

* Activar el interruptor de reset fuerza a que todos los LEDs se apaguen inmediatamente.

* Tensión de salida de Lógica Alta aprox. 5 V; Lógica Baja aprox. 0 V.

Público objetivo y nivel:

Estudiantes y aficionados familiarizados con niveles lógicos básicos que se inician en el diseño de lógica secuencial.

Materiales

- U1: 74HC161, función: CI contador binario síncrono de 4 bits

- V1: Fuente de alimentación de 5 V CC, función: fuente de alimentación principal

- V2: Fuente de tensión pulsada (0 V a 5 V), función: Señal de reloj (1 Hz para visualización)

- R1: Resistencia de 330 Ω, función: limitación de corriente para el LED Q0

- R2: Resistencia de 330 Ω, función: limitación de corriente para el LED Q1

- R3: Resistencia de 330 Ω, función: limitación de corriente para el LED Q2

- R4: Resistencia de 330 Ω, función: limitación de corriente para el LED Q3

- R5: Resistencia de 10 kΩ, función: pull-up para Master Reset

- D1: LED rojo, función: Indicador para Q0 (LSB)

- D2: LED rojo, función: Indicador para Q1

- D3: LED rojo, función: Indicador para Q2

- D4: LED rojo, función: Indicador para Q3 (MSB)

- S1: Pulsador momentáneo (normalmente abierto), función: disparador de Reset

Pin-out del CI utilizado

Chip seleccionado: 74HC161 (Contador Binario Síncrono de 4 bits, Reset Asíncrono)

| Pin | Nombre | Función lógica | Conexión en este caso |

|---|---|---|---|

| 1 | \overlineMR | Master Reset (Activo bajo) | Conectado al nodo Reset (S1/R5) |

| 2 | CP | Pulso de reloj (Flanco ascendente) | Conectado a V2 (Fuente de reloj) |

| 7 | CEP | Habilitación de conteo paralelo | Conectado a VCC (Siempre habilitado) |

| 8 | GND | Tierra | Conectado a 0 (GND) |

| 9 | \overlinePE | Habilitación paralela (Carga) | Conectado a VCC (Deshabilitado) |

| 10 | CET | Habilitación de conteo «Trickle» | Conectado a VCC (Siempre habilitado) |

| 11 | Q3 | Bit de salida 3 (MSB) | Conectado a D4 a través de R4 |

| 12 | Q2 | Bit de salida 2 | Conectado a D3 a través de R3 |

| 13 | Q1 | Bit de salida 1 | Conectado a D2 a través de R2 |

| 14 | Q0 | Bit de salida 0 (LSB) | Conectado a D1 a través de R1 |

| 16 | VCC | Alimentación (+5 V) | Conectado a VCC |

Nota: Los pines 3, 4, 5, 6 (Entradas de datos paralelos) y 15 (Salida de acarreo «Ripple Carry») no se utilizan en esta configuración básica de conteo y las entradas pueden conectarse a tierra si se prefiere, aunque normalmente son irrelevantes cuando la Carga (Load) está deshabilitada.

Guía de conexionado

Construya el circuito siguiendo estas conexiones de nodos explícitas:

-

Nodos de alimentación:

- Conecte el terminal positivo de

V1al nodoVCC. - Conecte el terminal negativo de

V1al nodo0(GND). - Conecte el pin 16 de

U1aVCC. - Conecte el pin 8 de

U1a0.

- Conecte el terminal positivo de

-

Entradas de control:

- Conecte el positivo de

V2(Fuente de reloj) al nodoCLK. Conecte el negativo deV2a0. - Conecte el pin 2 de

U1al nodoCLK. - Conecte los pines 7 (CEP), 10 (CET) y 9 (\overlinePE) de

U1directamente aVCCpara habilitar el conteo y deshabilitar la carga paralela. - Circuito de Reset: Conecte

R5entreVCCy el nodoRESET_N. ConecteS1entre el nodoRESET_Ny0. Conecte el pin 1 deU1aRESET_N.

- Conecte el positivo de

-

Salidas (Indicadores LED):

- Bit 0 (LSB): Conecte el pin 14 de

U1al nodoQ0. ConecteR1entreQ0y el nodoLED_A1. Conecte el ánodo deD1aLED_A1y el cátodo a0. - Bit 1: Conecte el pin 13 de

U1al nodoQ1. ConecteR2entreQ1y el nodoLED_A2. Conecte el ánodo deD2aLED_A2y el cátodo a0. - Bit 2: Conecte el pin 12 de

U1al nodoQ2. ConecteR3entreQ2y el nodoLED_A3. Conecte el ánodo deD3aLED_A3y el cátodo a0. - Bit 3 (MSB): Conecte el pin 11 de

U1al nodoQ3. ConecteR4entreQ3y el nodoLED_A4. Conecte el ánodo deD4aLED_A4y el cátodo a0.

- Bit 0 (LSB): Conecte el pin 14 de

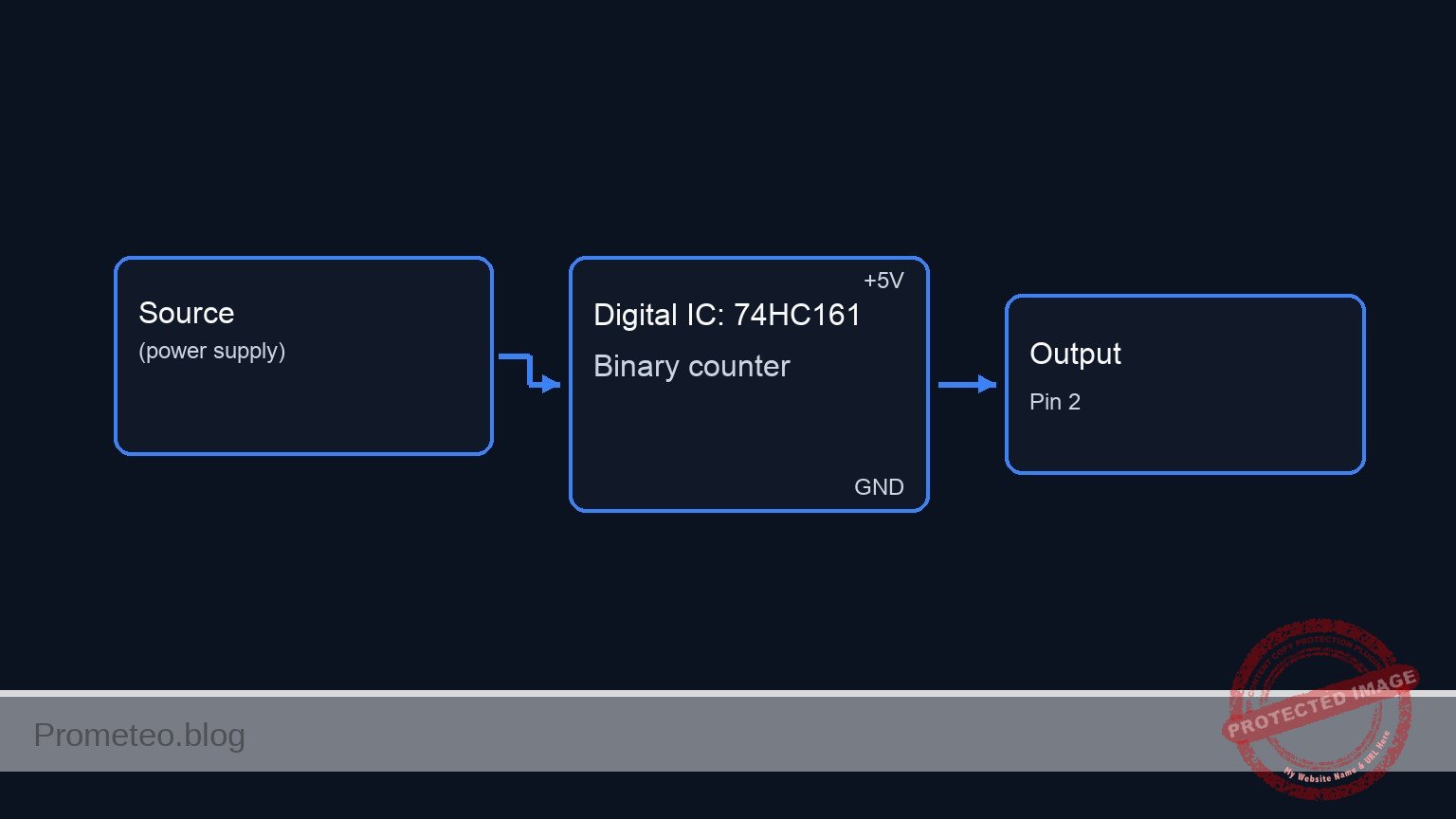

Diagrama de bloques conceptual

Esquemático

+-------------------------------------------------------------------------------------------------------+

| PRACTICAL CASE: 4-BIT UP COUNTER |

+-------------------------------------------------------------------------------------------------------+

INPUTS & CONTROL PROCESSING (U1) OUTPUTS & LOAD

(Left-to-Right Flow) (74HC161 Counter) (LED Visualization)

+-------------------------+

| |

[ V2: Clock Source ] --(CLK 1Hz)---> | [Pin 2] CP |

| |

| | (Bit 0 - LSB)

[ Reset Logic ] | [Pin 14] Q0 | --(Q0)--> [ R1: 330 ] --> [ D1: Red ] --> GND

(VCC->R5->Node->S1->GND) --(RST_N)-> | [Pin 1] ~MR |

| |

| | (Bit 1)

| [Pin 13] Q1 | --(Q1)--> [ R2: 330 ] --> [ D2: Red ] --> GND

[ VCC: 5 V Source ] --(Enable High)-> | [Pin 7] CEP |

--(Enable High)-> | [Pin 10] CET |

--(Disable Load)> | [Pin 9] ~PE | (Bit 2)

| [Pin 12] Q2 | --(Q2)--> [ R3: 330 ] --> [ D3: Red ] --> GND

| |

| |

| | (Bit 3 - MSB)

| [Pin 11] Q3 | --(Q3)--> [ R4: 330 ] --> [ D4: Red ] --> GND

| |

+-------------------------+

| |

[Pin 16] [Pin 8]

| |

VCC GND

Mediciones y pruebas

- Comprobación de alimentación: Antes de conectar el CI, mida la tensión entre

VCCy0para asegurarse de que sea estable a 5 V. - Verificación del reloj: Ajuste

V2a una frecuencia baja (p. ej., 1 Hz). Verifique que la señal en el nodoCLKoscila entre 0 V y 5 V. - Observación de la secuencia: Encienda el circuito. Observe de

D1aD4. Deberían alternar en la secuencia binaria:- 0: Todos APAGADOS

- 1: D1 ENCENDIDO

- 2: D2 ENCENDIDO

- 3: D1 y D2 ENCENDIDOS

- … hasta 15: Todos ENCENDIDOS.

- Prueba de Reset: Mientras el contador está funcionando, presione

S1. Todos los LEDs deben apagarse inmediatamente (Reset Asíncrono) o en el siguiente flanco de reloj (si se usa una variante de reset síncrono, aunque el Reset del 74HC161 estándar suele ser asíncrono). - Niveles lógicos: Use un multímetro para medir el nodo

Q3cuando D4 esté encendido. Debería leer cerca de 5 V (Lógica Alta).

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Practical case: 4-bit up counter with LEDs (74HC161)

* NGSPICE Netlist

* Requires XSPICE extensions

.width out=256

* --- Power Supplies ---

V1 VCC 0 DC 5

* Clock Source: 1 Hz Pulse (0V to 5V), 50% duty cycle

* Corrected to 1 Hz per BOM (Period = 1s, Pulse Width = 0.5s)

V2 CLK 0 PULSE(0 5 0 1u 1u 0.5 1)

* --- Reset Circuit ---

* Pull-up resistor for Master Reset

R5 VCC RESET_N 10k

* S1: Momentary Push Button (Normally Open)

* Implemented as a Voltage Controlled Switch driven by V_BTN source

S1 RESET_N 0 CTRL_RST 0 SW_BTN

* Button Actuator (Simulates a press at 8s for 1s duration to test reset)

V_BTN CTRL_RST 0 PULSE(0 1 8 1m 1m 1 20)

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Practical case: 4-bit up counter with LEDs (74HC161)

* NGSPICE Netlist

* Requires XSPICE extensions

.width out=256

* --- Power Supplies ---

V1 VCC 0 DC 5

* Clock Source: 1 Hz Pulse (0V to 5V), 50% duty cycle

* Corrected to 1 Hz per BOM (Period = 1s, Pulse Width = 0.5s)

V2 CLK 0 PULSE(0 5 0 1u 1u 0.5 1)

* --- Reset Circuit ---

* Pull-up resistor for Master Reset

R5 VCC RESET_N 10k

* S1: Momentary Push Button (Normally Open)

* Implemented as a Voltage Controlled Switch driven by V_BTN source

S1 RESET_N 0 CTRL_RST 0 SW_BTN

* Button Actuator (Simulates a press at 8s for 1s duration to test reset)

V_BTN CTRL_RST 0 PULSE(0 1 8 1m 1m 1 20)

.model SW_BTN sw(vt=0.5 ron=1 roff=10Meg)

* --- 74HC161 4-bit Binary Counter Subcircuit Instance ---

* Connections match Wiring Guide:

* Pin 1 (MR_N) -> RESET_N

* Pin 2 (CP) -> CLK

* Pin 3-6 (D0-D3) -> 0 (GND)

* Pin 7 (CEP) -> VCC

* Pin 8 (GND) -> 0

* Pin 9 (PE_N) -> VCC

* Pin 10 (CET) -> VCC

* Pin 11-14 (Q3-Q0) -> Output Nodes

* Pin 15 (TC) -> TC_NC (Floating)

* Pin 16 (VCC) -> VCC

XU1 RESET_N CLK 0 0 0 0 VCC 0 VCC VCC Q3 Q2 Q1 Q0 TC_NC VCC 74HC161

* --- LED Output Indicators ---

* Bit 0 (LSB)

R1 Q0 LED_A1 330

D1 LED_A1 0 LED_RED

* Bit 1

R2 Q1 LED_A2 330

D2 LED_A2 0 LED_RED

* Bit 2

R3 Q2 LED_A3 330

D3 LED_A3 0 LED_RED

* Bit 3 (MSB)

R4 Q3 LED_A4 330

D4 LED_A4 0 LED_RED

* --- Models ---

.model LED_RED D(Is=1e-14 Rs=5 N=2)

* --- Subcircuit Definition: 74HC161 ---

* Behavioral XSPICE implementation of a 4-bit Counter with Async Reset

.subckt 74HC161 MR_N CP D0 D1 D2 D3 CEP GND PE_N CET Q3 Q2 Q1 Q0 TC VCC

* XSPICE Models

.model adc_in adc_bridge(in_low=2.0 in_high=3.0)

.model dac_out dac_bridge(out_low=0.0 out_high=5.0)

.model dff_mod d_dff(rise_delay=10n fall_delay=10n)

.model inv_mod d_inverter(rise_delay=5n fall_delay=5n)

* Input Bridges (Analog to Digital)

A_IN [MR_N CP] [mr_dig cp_dig] adc_in

* Reset Logic (MR_N is active low, d_dff reset is active high)

A_RST_INV mr_dig rst_high inv_mod

* Counter Chain (Ripple Up Counter)

* Bit 0: Toggles on CP rising edge

A_D0 q0_inv cp_dig NULL rst_high q0_dig q0_inv dff_mod

* Bit 1: Toggles on Q0 falling edge (Q0_inv rising edge)

A_D1 q1_inv q0_inv NULL rst_high q1_dig q1_inv dff_mod

* Bit 2: Toggles on Q1 falling edge

A_D2 q2_inv q1_inv NULL rst_high q2_dig q2_inv dff_mod

* Bit 3: Toggles on Q2 falling edge

A_D3 q3_inv q2_inv NULL rst_high q3_dig q3_inv dff_mod

* Output Bridges (Digital to Analog)

A_OUT [q3_dig q2_dig q1_dig q0_dig] [Q3 Q2 Q1 Q0] dac_out

* Terminal Count (Unused/Dummy pull-down)

R_TC TC 0 100k

.ends

* --- Simulation Commands ---

* Transient analysis: 20s duration to capture full counting cycle (0-15) at 1 Hz

.op

.tran 10m 20s

* Print critical signals (Inputs first)

.print tran V(CLK) V(RESET_N) V(Q0) V(Q1) V(Q2) V(Q3)

.endResultados de Simulación (Transitorio)

Show raw data table (3020 rows)

Index time v(clk) v(reset_n) v(q0) v(q1) v(q2) v(q3) 0 0.000000e+00 0.000000e+00 4.995005e+00 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 1 1.000000e-08 5.000000e-02 4.995005e+00 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 2 2.000000e-08 1.000000e-01 4.995005e+00 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 3 4.000000e-08 2.000000e-01 4.995005e+00 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 4 8.000000e-08 4.000000e-01 4.995005e+00 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 5 1.600000e-07 8.000000e-01 4.995005e+00 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 6 3.200000e-07 1.600000e+00 4.995005e+00 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 7 6.400000e-07 3.200000e+00 4.995005e+00 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 8 6.520000e-07 3.260000e+00 4.995005e+00 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 9 6.760000e-07 3.380000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 10 7.240000e-07 3.620000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 11 8.200000e-07 4.100000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 12 1.000000e-06 5.000000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 13 1.019200e-06 5.000000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 14 1.057600e-06 5.000000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 15 1.134400e-06 5.000000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 16 1.288000e-06 5.000000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 17 1.595200e-06 5.000000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 18 2.209600e-06 5.000000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 19 3.438400e-06 5.000000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 20 5.896000e-06 5.000000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 21 1.081120e-05 5.000000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 22 2.064160e-05 5.000000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 23 4.030240e-05 5.000000e+00 4.995005e+00 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 ... (2996 more rows) ...

Errores comunes y cómo evitarlos

- Dejar los pines Enable flotando: La serie 74HC tiene entradas de alta impedancia. Si los pines 7 (CEP) o 10 (CET) no están conectados a VCC, el contador puede no contar o comportarse de manera errática. Siempre conecte las entradas de control no utilizadas a un nivel lógico definido.

- Frecuencia de reloj demasiado alta: Si

V2se ajusta a 1 kHz o más, todos los LEDs parecerán estar tenuemente encendidos de forma continua debido a la persistencia de la visión. Mantenga el reloj por debajo de 5 Hz para la depuración visual. - Pin de Carga Paralela flotante: Si el pin 9 (\overlinePE) se deja flotando o bajo, el chip podría intentar cargar constantemente datos desde las entradas P0-P3 en lugar de contar. Asegúrese de que el pin 9 esté conectado a VCC.

Solución de problemas

- Los LEDs nunca se encienden: Verifique las conexiones de alimentación a los pines 16 y 8. Asegúrese de que los LEDs estén insertados con la polaridad correcta (ánodo a resistencia/CI, cátodo a tierra).

- El contador se queda en cero: Verifique que el pin de Reset (1) esté Alto (5 V). Si

S1está atascado o falta la resistencia de pull-upR5, el chip permanece en estado de Reset. Además, verifique que los pines Enable (7, 10) estén Altos. - El contador salta números: Esto se debe a menudo al «rebote del interruptor» (switch bounce) si está utilizando un interruptor mecánico como reloj manual. Use un generador de onda cuadrada limpia o un circuito antirrebote (condensador + resistencia) para la entrada de reloj.

- Secuencia aleatoria: Verifique si el pin de Habilitación Paralela (\overlinePE) está accidentalmente Bajo o flotando. Debe estar Alto.

Posibles mejoras y extensiones

- Contador de 8 bits: Conecte en cascada un segundo 74HC161 conectando la Salida de Acarreo (pin 15) del primer contador a la Habilitación «Trickle» (pin 10) del segundo contador. Esto permite contar hasta 255.

- Reloj manual: Reemplace el generador de frecuencia

V2con un circuito temporizador 555 en modo astable o un pulsador con antirrebote para avanzar la cuenta manualmente.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.