Nivel: Medio

Diseña un circuito que disminuya la intensidad de la retroiluminación LED a medida que aumenta la luz ambiental.

Objetivo y caso de uso

En este caso práctico, construirás un controlador PWM (Modulación por Ancho de Pulso) utilizando un temporizador 555 y una fotorresistencia (LDR). El circuito ajustará automáticamente el ciclo de trabajo de la señal de salida basándose en los niveles de luz ambiental, controlando un MOSFET de potencia para atenuar una tira de LED.

Por qué es útil:

* Eficiencia energética: Reduce el consumo de energía en entornos de alto brillo donde la retroiluminación podría ser menos visible o necesaria (dependiendo del tipo de pantalla).

* Luces nocturnas automáticas: Útil para sistemas que necesitan ser tenues durante el día y brillantes por la noche (si se invierte la lógica) o viceversa.

* Confort visual humano: Previene el deslumbramiento ajustando la intensidad de la luz dinámicamente.

* Instrumentación: A menudo utilizado en tableros de automóviles o paneles de control.

Resultado esperado:

* Generación de señal: Una salida de onda cuadrada en el pin 3 del temporizador 555.

* Respuesta inversa: Cuando el LDR se expone a luz fuerte (Linterna), el brillo del LED disminuye.

* Respuesta en oscuridad: Cuando el LDR está cubierto (Oscuridad), el brillo del LED aumenta al máximo.

* Público objetivo: Estudiantes de electrónica de nivel intermedio y aficionados.

Materiales

- V1: Fuente de voltaje de 9 V CC, función: Alimentación principal del circuito.

- R1: Fotorresistencia (LDR), función: Sensor de luz (Ruta de carga).

- R2: Resistencia de 10 kΩ, función: Temporización de la ruta de descarga.

- R3: Resistencia de 1 kΩ, función: Protección de la Gate del MOSFET.

- R4: Resistencia de 330 Ω, función: Limitación de corriente del LED.

- C1: Condensador de 100 nF, función: Condensador de temporización PWM.

- C2: Condensador de 10 nF, función: Filtrado de ruido del voltaje de control.

- D1: Diodo 1N4148, función: Diodo de dirección para la ruta de carga.

- D2: Diodo 1N4148, función: Diodo de dirección para la ruta de descarga.

- D3: LED blanco de alto brillo, función: Retroiluminación simulada.

- Q1: 2N7000 (MOSFET de canal N), función: Interruptor controlador del LED.

- U1: Temporizador de precisión NE555, función: Generador PWM.

Guía de conexionado

Esta guía utiliza nombres de nodos específicos (VCC, 0, V_TRIG, V_GATE, etc.) para ayudarte a verificar las conexiones.

- Fuente de alimentación:

- Conecta el terminal positivo de V1 al nodo

VCC. - Conecta el terminal negativo de V1 al nodo

0(GND). - Alimentación y Reset del Temporizador 555 (U1):

- Conecta U1 pin 8 (VCC) al nodo

VCC. - Conecta U1 pin 1 (GND) al nodo

0. - Conecta U1 pin 4 (Reset) al nodo

VCC. - Red de temporización (El núcleo PWM):

- Conecta R1 (LDR) entre el nodo

VCCy el nodoV_CHARGE. - Conecta D1 (Ánodo) a

V_CHARGEy D1 (Cátodo) al nodoV_TIMING. - Conecta D2 (Ánodo) al nodo

V_TIMINGy D2 (Cátodo) al nodoV_DISCHARGE. - Conecta R2 entre el nodo

V_DISCHARGEy U1 pin 7 (Discharge). - Conecta C1 entre el nodo

V_TIMINGy el nodo0. - Conecta U1 pin 2 (Trigger) al nodo

V_TIMING. - Conecta U1 pin 6 (Threshold) al nodo

V_TIMING. - Voltaje de control:

- Conecta C2 entre U1 pin 5 (CV) y el nodo

0. - Etapa de salida:

- Conecta R3 entre U1 pin 3 (Output) y el nodo

V_GATE. - Conecta Q1 Gate al nodo

V_GATE. - Conecta Q1 Source al nodo

0. - Conecta Q1 Drain al nodo

V_LED_CATHODE. - Carga (Retroiluminación):

- Conecta R4 entre el nodo

VCCy el nodoV_LED_ANODE. - Conecta D3 Anode al nodo

V_LED_ANODE. - Conecta D3 Cathode al nodo

V_LED_CATHODE.

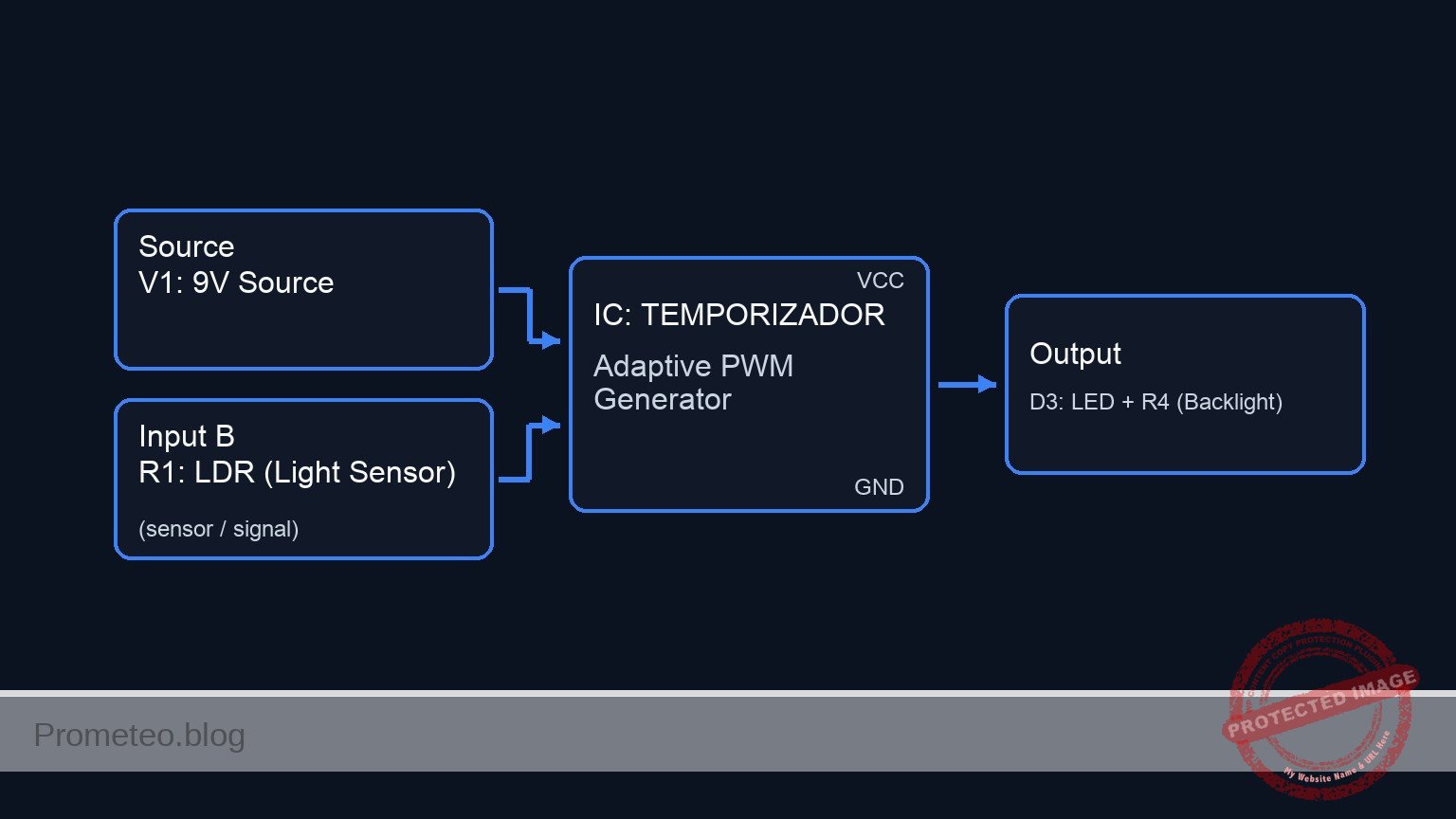

Diagrama de bloques conceptual

Esquemático

Title: Practical case: Adaptive Screen Brightness Regulator

[ INPUTS / TIMING NETWORK ] [ LOGIC / CONTROL ] [ OUTPUT STAGE ]

[ V1: 9 V Source ] --(Power VCC)--------->+-----------------------+

| |

(Light) -> [ R1: LDR ] --(Charge)------->| |

| U1: NE555 |

[ D1, D2, R2 ] --(Steering/Disch)------->| (PWM Generator) |--(Pin 3)--> [ R3: 1k ] --> [ Q1: MOSFET ]

| | |

[ C1: 100nF ] --(Timing Ramp)----------->| Pins 2,6 (Trig/Thr) | |

| Pin 7 (Discharge) | (Switches GND)

[ C2: 10nF ] --(Filter)----------------->| Pin 5 (Ctrl Volt) | |

| | v

+-----------------------+ [ D3: LED + R4: 330R ]

(Backlight)

Mediciones y pruebas

Realiza estos pasos para validar el comportamiento «Inverso» (Más luz = Menos brillo).

- Comprobación base (Luz ambiental):

- Alimenta el circuito con 9 V.

- Observa el LED D3. Debería estar iluminado a un nivel moderado.

- Mide el voltaje en

V_GATEusando un osciloscopio. Deberías ver una onda cuadrada.

- Prueba de luz alta:

- Apunta una linterna directamente sobre R1 (LDR).

- Observación: El LED D3 debería atenuarse significativamente o apagarse.

- Medición: Comprueba el ciclo de trabajo en

V_GATE. Dado que la resistencia del LDR cae, el condensador se carga muy rápidamente (Ton corto) en relación con el tiempo de descarga fijo (Toff). El Ciclo de Trabajo (Ton / Ttotal) disminuye.

- Prueba de luz baja:

- Cubre R1 (LDR) con tu mano o una tapa negra.

- Observación: El LED D3 debería alcanzar el brillo máximo.

- Medición: La resistencia del LDR aumenta, haciendo que el tiempo de carga (Ton) sea mucho más largo. El Ciclo de Trabajo aumenta hacia el 100%.

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Practical case: Adaptive Screen Brightness Regulator

* --- Power Supply ---

V1 VCC 0 DC 9

* --- Input Stage (Light Sensor) ---

R1 VCC V_CHARGE 20k

* --- PWM Timing Network ---

D1 V_CHARGE V_TIMING D1N4148

D2 V_TIMING V_DISCHARGE D1N4148

R2 V_DISCHARGE V_DISCH_PIN 10k

C1 V_TIMING 0 100n

* --- Control & Processing ---

* U1: NE555 Precision Timer

XU1 0 V_TIMING V_OUT_PIN VCC V_CV V_TIMING V_DISCH_PIN VCC NE555

* Control Voltage noise filtering

C2 V_CV 0 10n

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Practical case: Adaptive Screen Brightness Regulator

* --- Power Supply ---

V1 VCC 0 DC 9

* --- Input Stage (Light Sensor) ---

R1 VCC V_CHARGE 20k

* --- PWM Timing Network ---

D1 V_CHARGE V_TIMING D1N4148

D2 V_TIMING V_DISCHARGE D1N4148

R2 V_DISCHARGE V_DISCH_PIN 10k

C1 V_TIMING 0 100n

* --- Control & Processing ---

* U1: NE555 Precision Timer

XU1 0 V_TIMING V_OUT_PIN VCC V_CV V_TIMING V_DISCH_PIN VCC NE555

* Control Voltage noise filtering

C2 V_CV 0 10n

* --- Output Driver Stage ---

R3 V_OUT_PIN V_GATE 1k

* Q1: N-Channel MOSFET

MQ1 V_LED_CATHODE V_GATE 0 0 2N7000

* --- Load (Backlight) ---

R4 VCC V_LED_ANODE 330

D3 V_LED_ANODE V_LED_CATHODE WHITE_LED

* --- Component Models ---

.model D1N4148 D (IS=2.682n N=1.836 RS=.5664 BV=100 IBV=100p CJO=4p TT=11.54n)

.model 2N7000 NMOS (Level=1 VTO=2.1 KP=0.5 Lambda=0.002 RD=1.5 RS=1.5 CGSO=10p CGDO=10p CGBO=10p)

.model WHITE_LED D (IS=1p N=5 RS=5 BV=5 IBV=10u CJO=50p)

* --- NE555 Behavioral Subcircuit ---

.subckt NE555 GND TRIG OUT RESET CV THRES DISCH VCC

* Internal Voltage Divider

R_div1 VCC CV 5k

R_div2 CV TR 5k

R_div3 TR GND 5k

* Comparators (Sigmoid-based for smooth convergence)

* Set Signal (Active High) when TRIG < 1/3 VCC (V_TR)

B_set set_node 0 V = 2.5 + 2.5 * tanh(100 * (V(TR) - V(TRIG)))

* Reset Signal Logic

* Condition 1: THRES > CV

B_c1 c1 0 V = 0.5 * (1 + tanh(100 * (V(THRES) - V(CV))))

* Condition 2: RESET < 1.0V

B_c2 c2 0 V = 0.5 * (1 + tanh(100 * (1.0 - V(RESET))))

* Combine (Probabilistic OR logic): V_rst = c1 + c2 - c1*c2, scaled to 5V

B_rst rst_node 0 V = 5 * (V(c1) + V(c2) - V(c1)*V(c2))

* RC Delays to prevent algebraic loops in Flip-Flop

R_sd set_node set_d 1k

C_sd set_d 0 1p

R_rd rst_node rst_d 1k

C_rd rst_d 0 1p

* SR Latch (Cross-coupled NOR logic with soft thresholds)

* Q = ~(R | Qb)

B_q q_int 0 V = 5 / (1 + exp( 20 * (V(rst_d) + V(qb_int) - 2.5) ))

* Qb = ~(S | Q)

B_qb qb_int 0 V = 5 / (1 + exp( 20 * (V(set_d) + V(q_int) - 2.5) ))

* Output Buffer

E_out OUT_int 0 q_int 0 1

R_out_prot OUT_int OUT 1

* Discharge Transistor (Switch to GND when Qb is High / Output Low)

S_disch DISCH 0 qb_int 0 SW_DISCH

.model SW_DISCH SW(Vt=2.5 Ron=10 Roff=100Meg)

.ends

* --- Simulation Directives ---

.tran 10u 20m

.print tran V(V_TIMING) V(V_GATE) V(V_LED_CATHODE) V(V_LED_ANODE)

.op

.endResultados de Simulación (Transitorio)

Show raw data table (4016 rows)

Index time v(v_timing) v(v_gate) v(v_led_cathode 0 0.000000e+00 3.183820e+00 9.643749e-22 8.709822e+00 1 1.000000e-07 3.183820e+00 9.643749e-22 8.709822e+00 2 2.000000e-07 3.183820e+00 -2.54330e-17 8.709822e+00 3 4.000000e-07 3.183820e+00 4.759196e-18 8.709822e+00 4 8.000000e-07 3.183820e+00 -5.90561e-18 8.709822e+00 5 1.600000e-06 3.183820e+00 1.843922e-17 8.709822e+00 6 3.200000e-06 3.183820e+00 4.911091e-18 8.709822e+00 7 6.400000e-06 3.183819e+00 9.652751e-18 8.709822e+00 8 1.280000e-05 3.183819e+00 -2.42211e-18 8.709822e+00 9 2.280000e-05 3.183818e+00 -2.25892e-17 8.709822e+00 10 3.280000e-05 3.183818e+00 -5.29878e-18 8.709822e+00 11 4.280000e-05 3.183817e+00 -8.38426e-18 8.709822e+00 12 5.280000e-05 3.183816e+00 -5.24090e-18 8.709822e+00 13 6.280000e-05 3.183815e+00 5.344924e-18 8.709822e+00 14 7.280000e-05 3.183815e+00 -6.20163e-18 8.709822e+00 15 8.280000e-05 3.183814e+00 -2.95146e-18 8.709822e+00 16 9.280000e-05 3.183813e+00 -1.95605e-17 8.709822e+00 17 1.028000e-04 3.183813e+00 5.833300e-18 8.709822e+00 18 1.128000e-04 3.183812e+00 -9.79628e-18 8.709822e+00 19 1.228000e-04 3.183812e+00 1.090495e-18 8.709822e+00 20 1.328000e-04 3.183811e+00 -1.79618e-17 8.709822e+00 21 1.428000e-04 3.183810e+00 6.632650e-18 8.709822e+00 22 1.528000e-04 3.183810e+00 -1.47697e-17 8.709822e+00 23 1.628000e-04 3.183809e+00 6.958764e-18 8.709822e+00 ... (3992 more rows) ...

Errores comunes y cómo evitarlos

- Invertir los diodos de dirección (D1, D2):

- Error: Colocar D1 o D2 al revés impide que el condensador se cargue o descargue correctamente.

- Solución: Asegúrate de que la banda negra (cátodo) de D1 apunte hacia el condensador y la banda negra de D2 apunte hacia el Pin 7.

- Conectar el LDR al Pin 7 directamente:

- Error: Conectar el LDR sin los diodos de dirección crea un oscilador astable estándar donde la frecuencia cambia drásticamente, pero el control del ciclo de trabajo es menos distintivo.

- Solución: Utiliza la topología de dirección con diodos descrita para separar las rutas de Carga (LDR) y Descarga (R2).

- Confusión en el pinout del MOSFET:

- Error: Intercambiar Drain y Source en el 2N7000.

- Solución: Verifica la hoja de datos. Para el 2N7000 (TO-92), mirando el lado plano, los pines suelen ser Source, Gate, Drain (de izquierda a derecha).

Solución de problemas

- Síntoma: El LED está siempre ENCENDIDO y no cambia con la luz.

- Causa: Gate del MOSFET flotante o Pin 3 atascado en Alto.

- Arreglo: Revisa las conexiones de R1 y C1. Asegúrate de que los pines 2 y 6 estén unidos.

- Síntoma: El LED está siempre APAGADO.

- Causa: La resistencia del LDR es demasiado baja (cortocircuito) o el LED está conectado al revés.

- Arreglo: Revisa la polaridad del LED. Mide la resistencia del LDR en oscuridad; si es 0 Ω, está defectuoso.

- Síntoma: El LED parpadea visiblemente.

- Causa: La frecuencia es demasiado baja.

- Arreglo: Reduce el valor de C1 (p. ej., cambia de 100 nF a 10 nF) para aumentar la frecuencia PWM más allá de la persistencia de la visión humana (> 100 Hz).

Posibles mejoras y extensiones

- Fijación de brillo mínimo: Añade una resistencia fija en serie con el LDR (R1). Esto asegura que incluso con luz extremadamente brillante (baja resistencia del LDR), todavía haya un tiempo de carga mínimo, evitando que el LED se apague por completo.

- Transición más suave: Añade un condensador grande en paralelo con el LDR para filtrar cambios rápidos en la luz (p. ej., sombras de objetos que pasan), creando un efecto de «desvanecimiento» en lugar de un salto instantáneo en el brillo.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.