Nivel: Avanzado. Implementar un circuito de reloj controlado (clock gating) que permita pulsos de sincronización solo cuando Data Ready y System Enable estén activos.

Objetivo y caso de uso

En esta sesión, diseñará y analizará un circuito de gating de reloj (clock gating) utilizando puertas AND en cascada para controlar el flujo de pulsos de reloj de alta velocidad hacia un registro de desplazamiento. Validará que la señal de reloj solo se propague cuando dos banderas de control distintas (‘Data Ready’ y ‘System Enable’) estén simultáneamente en alto.

Por qué es útil:

* Gestión de energía: Deshabilitar el árbol de reloj hacia registros de desplazamiento inactivos o subsistemas reduce el consumo de energía dinámica en circuitos CMOS.

* Integridad de datos: Asegura que los datos solo se registren en el búfer cuando la fuente indica datos válidos (Data Ready) y el controlador permite la recepción (System Enable).

* Arbitraje de bus: Previene la contención del bus sincronizando múltiples periféricos que comparten una línea de datos común.

Resultado esperado:

* La salida GATED_CLK refleja la entrada CLK solo cuando DATA_RDY = 1 y SYS_EN = 1.

* Se mide el retardo de propagación entre el flanco de reloj de entrada y el flanco de reloj de salida (típicamente 7–15 ns para la serie 74HC).

* Identificación de «pulsos enanos» (runt pulses) o glitches si las señales de habilitación cambian de estado mientras el reloj está en alto.

Público objetivo y nivel:

Estudiantes de ingeniería electrónica y diseñadores de sistemas embebidos (Avanzado).

Materiales

- U1: CI 74HC08 de cuatro puertas AND de 2 entradas, función: puerta lógica

- V_CLK: Generador de pulsos, función: Reloj Maestro (1 MHz, 0V-5V)

- V_DR: Fuente de tensión CC o Interruptor, función: señal Data Ready

- V_SE: Fuente de tensión CC o Interruptor, función: señal System Enable

- V1: Fuente de alimentación de 5 V CC, función: alimentación principal

- C1: Condensador cerámico de 100 nF, función: desacoplo de U1

- R_LOAD: Resistencia de 10 kΩ, función: simula impedancia de entrada del registro de desplazamiento

- C_LOAD: Condensador de 15 pF, función: simula capacitancia de entrada y carga de la sonda

Pin-out del CI utilizado

Chip seleccionado: 74HC08 (Cuádruple puerta AND de 2 entradas)

| Pin | Nombre | Función lógica | Conexión en este caso |

|---|---|---|---|

| 1 | 1A | Entrada Puerta 1 | Conecta al Nodo DATA_RDY |

| 2 | 1B | Entrada Puerta 1 | Conecta al Nodo SYS_EN |

| 3 | 1Y | Salida Puerta 1 | Conecta al Nodo ENABLE_COMBINED (Interno) |

| 4 | 2A | Entrada Puerta 2 | Conecta al Nodo ENABLE_COMBINED |

| 5 | 2B | Entrada Puerta 2 | Conecta al Nodo CLK_IN |

| 6 | 2Y | Salida Puerta 2 | Conecta al Nodo GATED_CLK |

| 7 | GND | Tierra / Masa | Conecta al Nodo 0 |

| 14 | VCC | Alimentación | Conecta al Nodo VCC |

Guía de conexionado

Construya el circuito siguiendo estas conexiones de nodos. Asegúrese de que la fuente de alimentación esté apagada mientras realiza el cableado.

-

Fuente de alimentación:

- El terminal positivo de

V1conecta al nodoVCC. - El terminal negativo de

V1conecta al nodo0(GND). C1conecta entreVCCy0(colocado cerca de U1).- El Pin 14 de

U1conecta aVCC. - El Pin 7 de

U1conecta a0.

- El terminal positivo de

-

Lógica de control (Puerta 1):

- El terminal positivo de

V_DR(Data Ready) conecta al nodoDATA_RDY. - El terminal positivo de

V_SE(System Enable) conecta al nodoSYS_EN. - El Pin 1 (1A) de

U1conecta al nodoDATA_RDY. - El Pin 2 (1B) de

U1conecta al nodoSYS_EN. - El Pin 3 (1Y) de

U1conecta al nodoENABLE_COMBINED.

- El terminal positivo de

-

Gating de reloj (Puerta 2):

- El terminal positivo de

V_CLK(Fuente de reloj) conecta al nodoCLK_IN. - El Pin 4 (2A) de

U1conecta al nodoENABLE_COMBINED. - El Pin 5 (2B) de

U1conecta al nodoCLK_IN. - El Pin 6 (2Y) de

U1conecta al nodoGATED_CLK.

- El terminal positivo de

-

Carga de salida:

R_LOADconecta entreGATED_CLKy0.C_LOADconecta entreGATED_CLKy0.

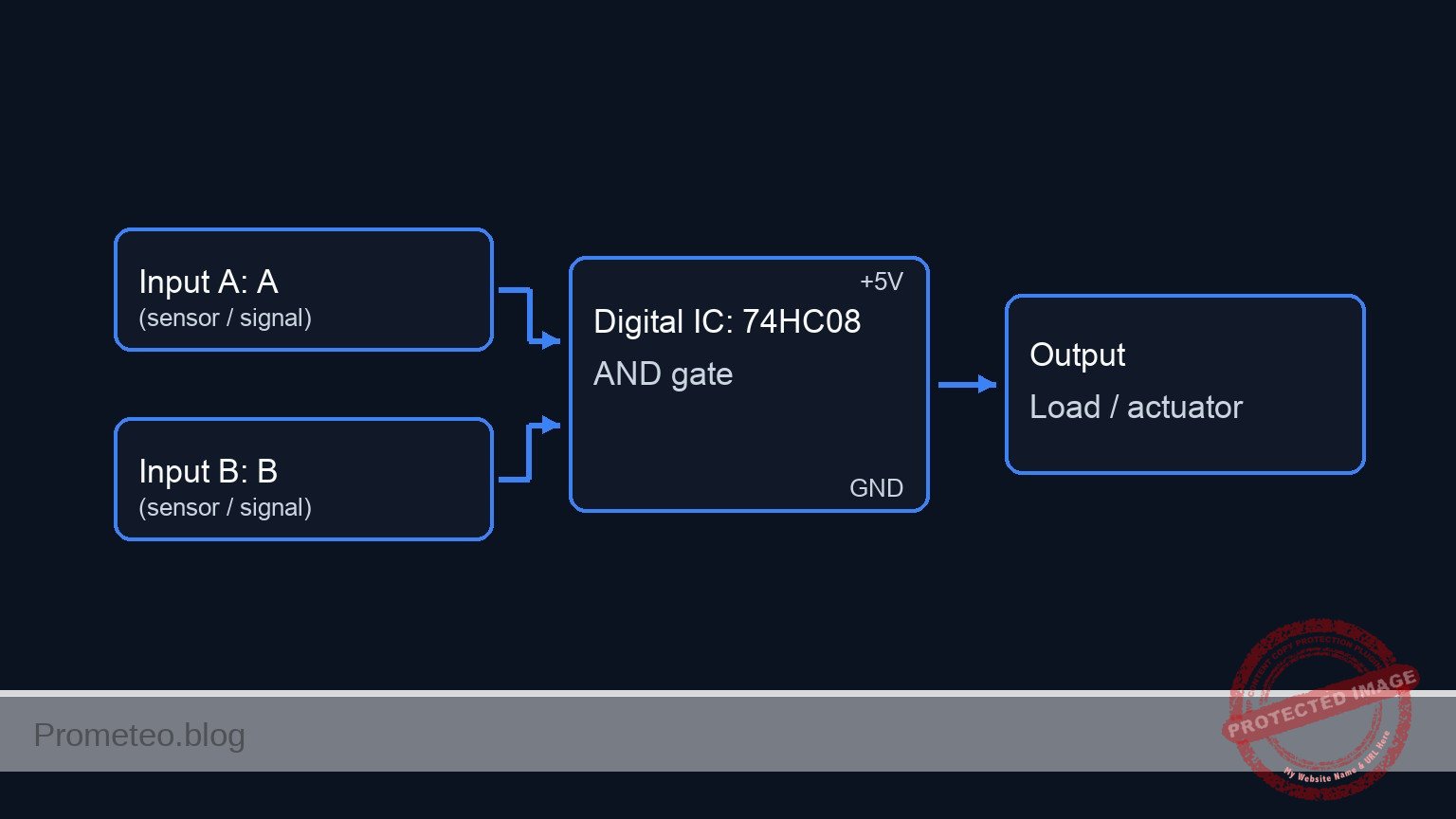

Diagrama de bloques conceptual

Esquemático

[ INPUT SIGNALS ] [ LOGIC PROCESSING (U1: 74HC08) ] [ OUTPUT STAGE ]

+-----------------------------------+

| POWER SUPPLY & DECOUPLING |

| V1 (5V) -> Pin 14, GND -> Pin 7 |

| C1 (100nF) across VCC/GND |

+-----------------------------------+

|

[ V_DR: Data Ready ] --(Pin 1)-->+ |

| v

+-----> [ AND Gate 1 ] ---+

| (Control Logic) |

[ V_SE: Sys Enable ] --(Pin 2)-->+ |

|

| (Pin 3: ENABLE_COMBINED)

|

v

(Pin 4)

+---> [ AND Gate 2 ] --(Pin 6)--> [ R_LOAD (10k) ] --+

| (Clock Gating) [ C_LOAD (15pF) ] |

[ V_CLK: Master Clk ] --(Pin 5)----------------------------+ (Signal: GATED_CLK) v

GND

Tabla de verdad

Esta tabla representa la lógica en cascada: GATED_CLK = (DATA_RDY AND SYS_EN) AND CLK_IN.

| DATA_RDY | SYS_EN | ENABLE_COMBINED (Interno) | CLK_IN | GATED_CLK | Descripción del estado |

|---|---|---|---|---|---|

| 0 | X | 0 | X | 0 | Bloqueado: Datos no listos |

| X | 0 | 0 | X | 0 | Bloqueado: Sistema deshabilitado |

| 1 | 1 | 1 | 0 | 0 | Activo: Fase baja del reloj |

| 1 | 1 | 1 | 1 | 1 | Activo: Fase alta del reloj aprobada |

(X = No importa)

Mediciones y pruebas

Realice los siguientes pasos de validación utilizando un osciloscopio (se recomienda doble canal).

-

Validación lógica estática:

- Establezca

V_CLKa 0V. ConmuteV_DRyV_SE. Asegúrese de queGATED_CLKpermanezca en 0V. - Establezca

V_CLKa 5V (CC). Asegúrese de queGATED_CLKesté en Alto SOLO cuando tantoV_DRcomoV_SEestén en Alto.

- Establezca

-

Gating de reloj dinámico:

- Configure

V_CLKa una onda cuadrada de 1 MHz (ciclo de trabajo del 50%). - Habilite el Canal 1 en

CLK_INy el Canal 2 enGATED_CLK. - Active tanto

V_DRcomoV_SE. Verifique que el Canal 2 replique al Canal 1. - Desactive

V_DR. Verifique que el Canal 2 se quede plano en Bajo.

- Configure

-

Análisis del retardo de propagación (Avanzado):

- Con el reloj funcionando y pasando a través, maximice el zoom horizontal (base de tiempo ~10ns/div).

- Mida la diferencia de tiempo entre el punto de tensión del 50% del flanco de subida de

CLK_INy el flanco de subida deGATED_CLK. - Resultado esperado: Un retardo de aproximadamente 15ns–25ns (suma de los retardos a través de la Puerta 1 y la Puerta 2).

-

Observación de Glitch/Riesgos:

- Mientras

CLK_INestá en Alto, conmute manualmenteDATA_RDY. - Observe si aparecen pulsos truncados («enanos» o runts) en la salida. Estos son riesgos causados por el gating asíncrono.

- Mientras

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Practical case: Data transfer synchronization

* --- Power Supply ---

* V1 positive terminal connects to node VCC. Negative to node 0 (GND).

V1 VCC 0 DC 5

* C1 connects between VCC and 0 (placed close to U1).

C1 VCC 0 100n

* --- Input Stimuli (Dynamic) ---

* V_CLK: Master Clock (1 MHz, 0V-5V).

* PULSE(V1 V2 TD TR TF PW PER) -> 1us Period, 0.49us Width

V_CLK CLK_IN 0 PULSE(0 5 0 10n 10n 490n 1u)

* V_DR: Data Ready signal.

* Simulates a data packet ready signal. Pulses High from 5us to 15us.

V_DR DATA_RDY 0 PULSE(0 5 5u 10n 10n 10u 40u)

* V_SE: System Enable signal.

* Simulates system enable window. Pulses High from 2us to 22us.

V_SE SYS_EN 0 PULSE(0 5 2u 10n 10n 20u 50u)

* --- Control Logic (U1: 74HC08) ---

* Instantiation of the IC using a behavioral subcircuit.

* Mapping pins according to Wiring Guide:

* Pin 1 (1A) -> DATA_RDY

* Pin 2 (1B) -> SYS_EN

* Pin 3 (1Y) -> ENABLE_COMBINED

* Pin 4 (2A) -> ENABLE_COMBINED

* Pin 5 (2B) -> CLK_IN

* Pin 6 (2Y) -> GATED_CLK

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Practical case: Data transfer synchronization

* --- Power Supply ---

* V1 positive terminal connects to node VCC. Negative to node 0 (GND).

V1 VCC 0 DC 5

* C1 connects between VCC and 0 (placed close to U1).

C1 VCC 0 100n

* --- Input Stimuli (Dynamic) ---

* V_CLK: Master Clock (1 MHz, 0V-5V).

* PULSE(V1 V2 TD TR TF PW PER) -> 1us Period, 0.49us Width

V_CLK CLK_IN 0 PULSE(0 5 0 10n 10n 490n 1u)

* V_DR: Data Ready signal.

* Simulates a data packet ready signal. Pulses High from 5us to 15us.

V_DR DATA_RDY 0 PULSE(0 5 5u 10n 10n 10u 40u)

* V_SE: System Enable signal.

* Simulates system enable window. Pulses High from 2us to 22us.

V_SE SYS_EN 0 PULSE(0 5 2u 10n 10n 20u 50u)

* --- Control Logic (U1: 74HC08) ---

* Instantiation of the IC using a behavioral subcircuit.

* Mapping pins according to Wiring Guide:

* Pin 1 (1A) -> DATA_RDY

* Pin 2 (1B) -> SYS_EN

* Pin 3 (1Y) -> ENABLE_COMBINED

* Pin 4 (2A) -> ENABLE_COMBINED

* Pin 5 (2B) -> CLK_IN

* Pin 6 (2Y) -> GATED_CLK

* Pin 7 (GND)-> 0

* Pin 14(VCC)-> VCC

XU1 DATA_RDY SYS_EN ENABLE_COMBINED ENABLE_COMBINED CLK_IN GATED_CLK 0 VCC 74HC08_BEHAVIORAL

* --- Output Loading ---

* R_LOAD connects between GATED_CLK and 0.

R_LOAD GATED_CLK 0 10k

* C_LOAD connects between GATED_CLK and 0.

C_LOAD GATED_CLK 0 15p

* --- Subcircuit Model: 74HC08 ---

* Robust behavioral implementation using sigmoid functions for convergence.

* Only the gates used in the wiring are modeled to save complexity.

.subckt 74HC08_BEHAVIORAL 1A 1B 1Y 2A 2B 2Y GND VCC

* Gate 1: 1Y = 1A AND 1B

* Function: V(VCC) * Sigmoid(A) * Sigmoid(B)

B_G1 1Y_INT GND V = V(VCC) * (1 / (1 + exp(-50*(V(1A)-2.5)))) * (1 / (1 + exp(-50*(V(1B)-2.5))))

R_G1 1Y_INT 1Y 100

* Gate 2: 2Y = 2A AND 2B

B_G2 2Y_INT GND V = V(VCC) * (1 / (1 + exp(-50*(V(2A)-2.5)))) * (1 / (1 + exp(-50*(V(2B)-2.5))))

R_G2 2Y_INT 2Y 100

.ends

* --- Analysis Directives ---

.op

* Transient analysis: 10ns step, 25us duration to capture full logic sequence

.tran 10n 25u

* --- Output Directives ---

.print tran V(CLK_IN) V(DATA_RDY) V(SYS_EN) V(ENABLE_COMBINED) V(GATED_CLK)

.endResultados de Simulación (Transitorio)

Show raw data table (6072 rows)

Index time v(clk_in) v(data_rdy) v(sys_en) 0 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 1 1.000000e-10 5.000000e-02 0.000000e+00 0.000000e+00 2 2.000000e-10 1.000000e-01 0.000000e+00 0.000000e+00 3 4.000000e-10 2.000000e-01 0.000000e+00 0.000000e+00 4 8.000000e-10 4.000000e-01 0.000000e+00 0.000000e+00 5 1.600000e-09 8.000000e-01 0.000000e+00 0.000000e+00 6 3.200000e-09 1.600000e+00 0.000000e+00 0.000000e+00 7 6.400000e-09 3.200000e+00 0.000000e+00 0.000000e+00 8 1.000000e-08 5.000000e+00 0.000000e+00 0.000000e+00 9 1.064000e-08 5.000000e+00 0.000000e+00 0.000000e+00 10 1.192000e-08 5.000000e+00 0.000000e+00 0.000000e+00 11 1.448000e-08 5.000000e+00 0.000000e+00 0.000000e+00 12 1.960000e-08 5.000000e+00 0.000000e+00 0.000000e+00 13 2.960000e-08 5.000000e+00 0.000000e+00 0.000000e+00 14 3.960000e-08 5.000000e+00 0.000000e+00 0.000000e+00 15 4.960000e-08 5.000000e+00 0.000000e+00 0.000000e+00 16 5.960000e-08 5.000000e+00 0.000000e+00 0.000000e+00 17 6.960000e-08 5.000000e+00 0.000000e+00 0.000000e+00 18 7.960000e-08 5.000000e+00 0.000000e+00 0.000000e+00 19 8.960000e-08 5.000000e+00 0.000000e+00 0.000000e+00 20 9.960000e-08 5.000000e+00 0.000000e+00 0.000000e+00 21 1.096000e-07 5.000000e+00 0.000000e+00 0.000000e+00 22 1.196000e-07 5.000000e+00 0.000000e+00 0.000000e+00 23 1.296000e-07 5.000000e+00 0.000000e+00 0.000000e+00 ... (6048 more rows) ...

Errores comunes y cómo evitarlos

- Dejar entradas no utilizadas flotando:

- Problema: Las entradas no utilizadas en el 74HC08 (p. ej., Pines 9, 10, 12, 13) captan ruido, causando alto consumo de energía u oscilación.

- Solución: Conecte todas las entradas de puertas AND no utilizadas directamente a GND o VCC.

- Ignorar la acumulación del retardo de propagación:

- Problema: Asumir que la salida ocurre instantáneamente. En esta configuración en cascada (Puerta 1 -> Puerta 2), el retardo es el doble que el de una sola puerta.

- Solución: Tenga en cuenta este retardo en los diagramas de tiempo; las señales pueden llegar demasiado tarde para el tiempo de establecimiento (setup time) del registro de desplazamiento subsiguiente.

- Hacer gating del reloj de forma asíncrona:

- Problema: Cambiar

SYS_ENmientras el reloj está en Alto recorta el ancho del pulso, violando el requisito de ancho de pulso mínimo del registro de desplazamiento. - Solución: Idealmente, sincronice la señal de Habilitación (Enable) con el flanco de bajada del reloj (usando un Flip-Flop) antes de alimentarla a la puerta AND.

- Problema: Cambiar

Solución de problemas

- Síntoma: La salida está permanentemente en Bajo, incluso cuando todas las entradas están en Alto.

- Causa: Falta alimentación en el Pin 14 o GND en el Pin 7.

- Solución: Verifique la continuidad de VCC/GND con un multímetro.

- Síntoma: «Fantasma» (ghosting) o flancos ruidosos en el osciloscopio.

- Causa: Falta de condensador de desacoplo o cables de tierra largos en las sondas.

- Solución: Instale C1 (100nF) extremadamente cerca del CI; use el muelle de tierra en la punta de la sonda.

- Síntoma: Los flancos de la señal son muy redondeados (tiempo de subida lento).

- Causa: La carga capacitiva es demasiado alta (cables largos o capacitancia parásita de la protoboard).

- Solución: Acorte los cables o añada un búfer si maneja una carga pesada.

Posibles mejoras y extensiones

- Gating libre de glitches: Añada un D-Flip-Flop (p. ej., 74HC74) para sincronizar la señal

ENABLE_COMBINEDde modo que solo cambie de estado cuando el Reloj esté en Bajo. - Inserción de estados de espera: Expanda el circuito para afirmar una señal «BUSY» de vuelta al controlador siempre que el reloj se active con éxito, confirmando que la transferencia de datos está activa.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.