Nivel: Medio. Diseñar un oscilador astable NE555 donde una LDR modula la frecuencia de salida en función de la luz ambiental.

Objetivo y caso de uso

En este proyecto, construirás un oscilador astable utilizando el CI temporizador 555, donde una resistencia dependiente de la luz (LDR) sustituye a una de las resistencias de temporización estándar. Esta sustitución cambia dinámicamente el tono de un altavoz piezoeléctrico dependiendo de la cantidad de luz que incide sobre el sensor.

Este circuito es muy útil en el mundo real:

* Sirve como sensor auditivo para advertencias luminosas, como una alarma para la puerta de un refrigerador que se ha quedado abierta.

* Actúa como un bloque de construcción fundamental para instrumentos musicales electrónicos sencillos, como un theremín óptico básico.

* Proporciona indicadores de accesibilidad, ofreciendo una retroalimentación de audio distintiva para que los usuarios con discapacidad visual sepan si las luces están encendidas o apagadas en una habitación.

* Demuestra cómo convertir una propiedad física analógica variable (luminosidad) en una señal eléctrica modulada en frecuencia.

Resultado esperado:

* El altavoz piezoeléctrico emitirá un tono continuo y audible.

* La frecuencia (tono) del sonido aumentará significativamente cuando la LDR se exponga a luz brillante.

* La frecuencia del sonido caerá a un tono más grave cuando la LDR esté cubierta o en un entorno oscuro.

* El condensador de temporización principal se cargará y descargará continuamente entre 1/3 y 2/3 del voltaje de alimentación.

Público objetivo y nivel: Estudiantes de electrónica de nivel intermedio que buscan combinar sensores analógicos con CIs de temporización estándar.

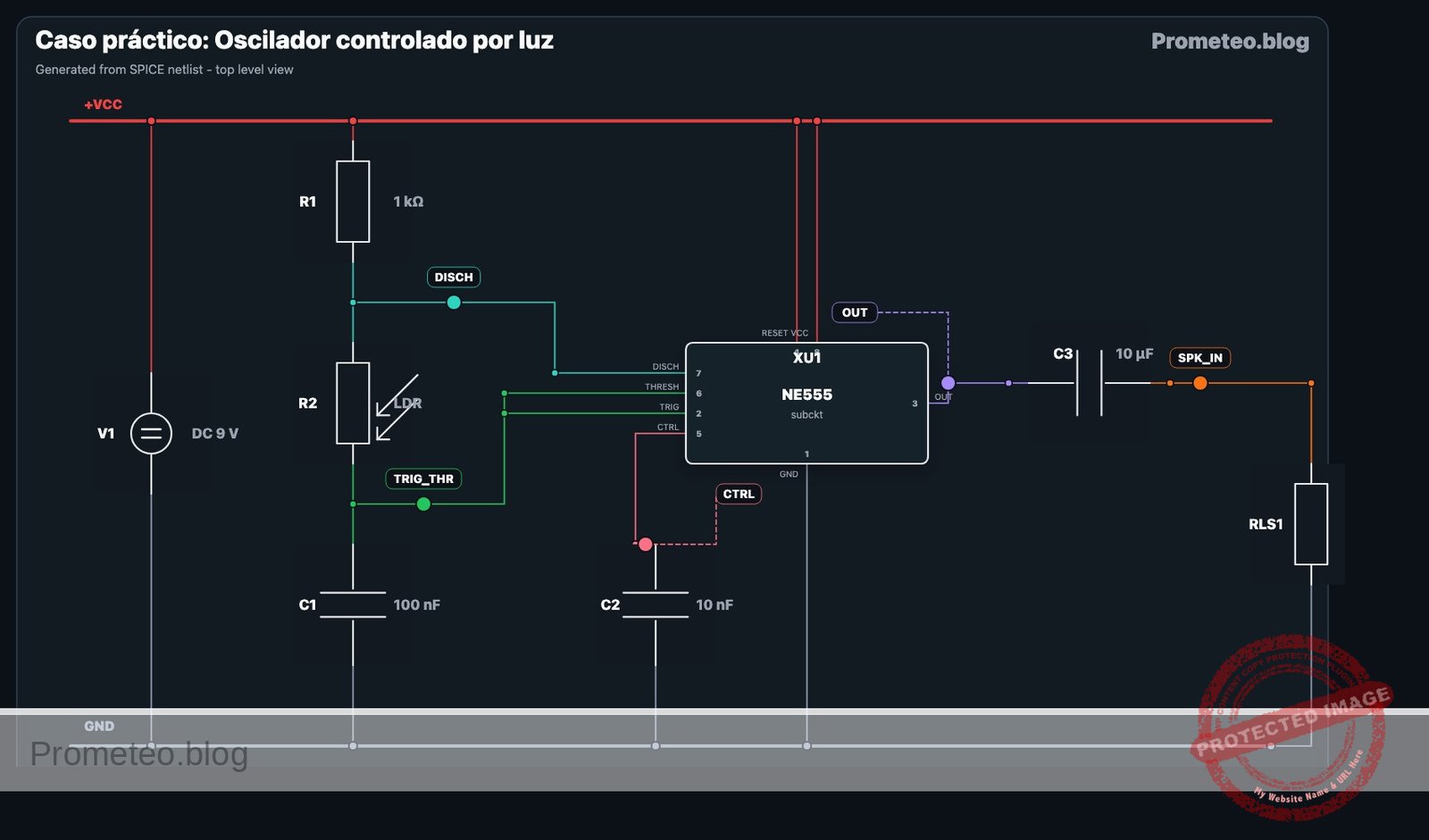

Materiales

V1: Fuente de alimentación de 9 V CCU1: CI temporizador NE555, función: oscilador astableR1: Resistencia de 1 kΩ, función: resistencia de temporización fija que limita la corriente de descargaR2: Fotorresistencia (LDR), función: resistencia de temporización variable modulada por luzC1: Condensador cerámico de 100 nF, función: condensador principal de temporización del osciladorC2: Condensador cerámico de 10 nF, función: estabilización del voltaje de control para U1C3: Condensador electrolítico de 10 µF, función: acoplamiento de CA para el altavozLS1: Altavoz piezoeléctrico, función: salida de audio

Guía de conexionado

V1: se conecta entre el nodoVCCy el nodo0(GND).U1Pin 1 (GND): se conecta al nodo0.U1Pin 8 (VCC): se conecta al nodoVCC.U1Pin 4 (RESET): se conecta al nodoVCC.U1Pin 7 (DISCHARGE): se conecta al nodoDISCH.U1Pin 2 (TRIGGER): se conecta al nodoTRIG_THR.U1Pin 6 (THRESHOLD): se conecta al nodoTRIG_THR.U1Pin 5 (CONTROL): se conecta al nodoCTRL.U1Pin 3 (OUTPUT): se conecta al nodoOUT.R1: se conecta entre el nodoVCCy el nodoDISCH.R2: se conecta entre el nodoDISCHy el nodoTRIG_THR.C1: se conecta entre el nodoTRIG_THRy el nodo0.C2: se conecta entre el nodoCTRLy el nodo0.C3: se conecta entre el nodoOUT(terminal positivo) y el nodoSPK_IN(terminal negativo).LS1: se conecta entre el nodoSPK_INy el nodo0.

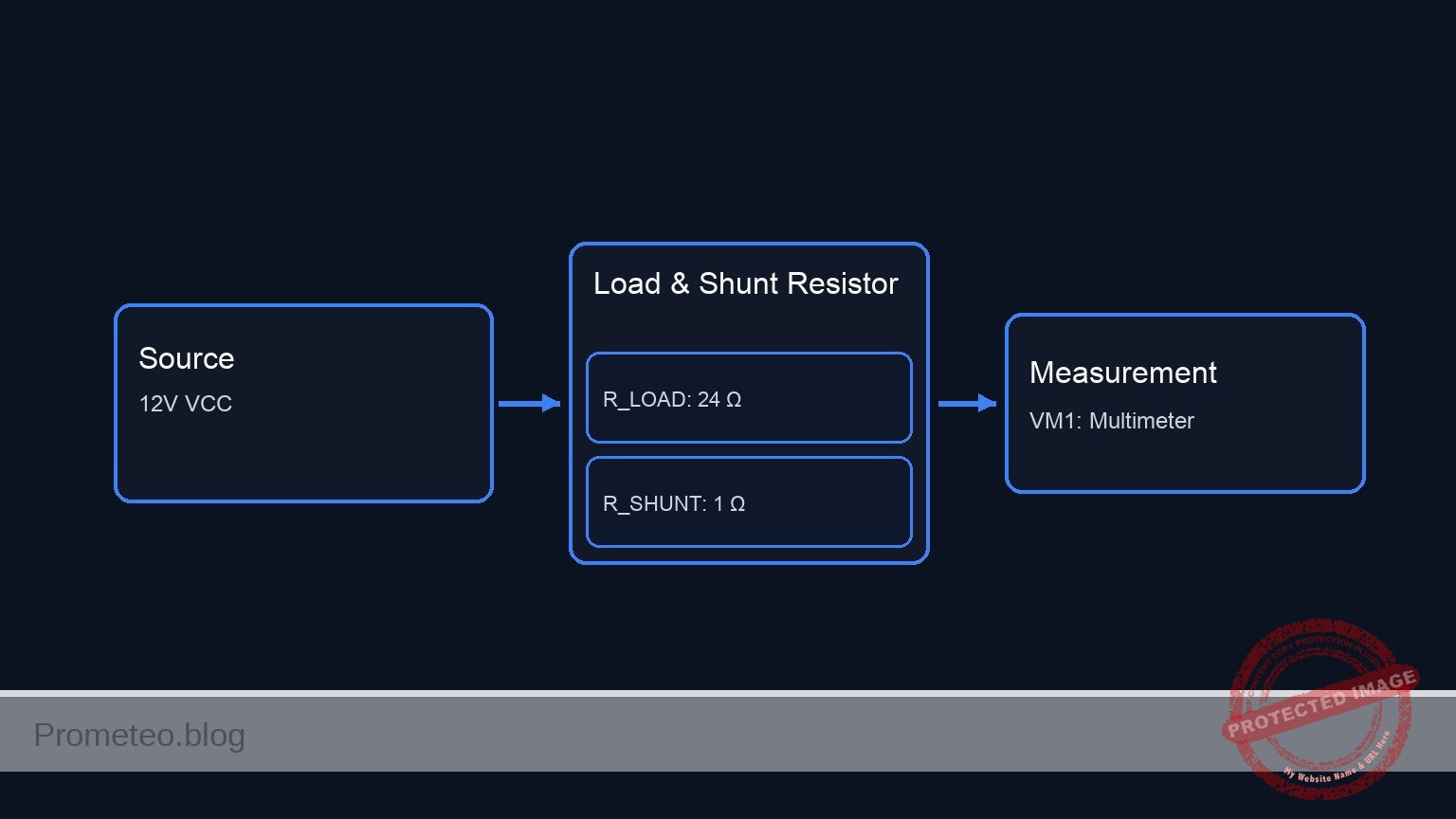

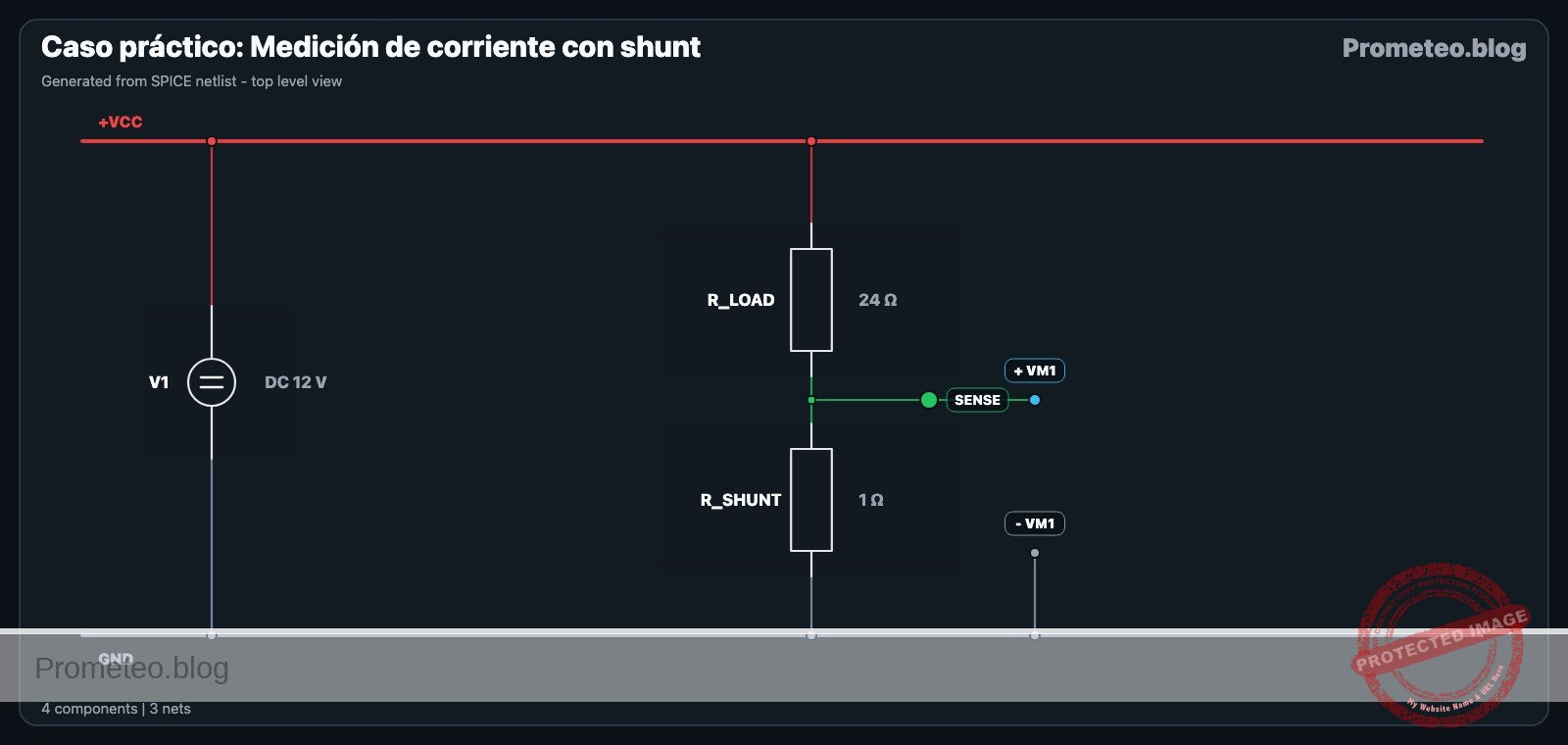

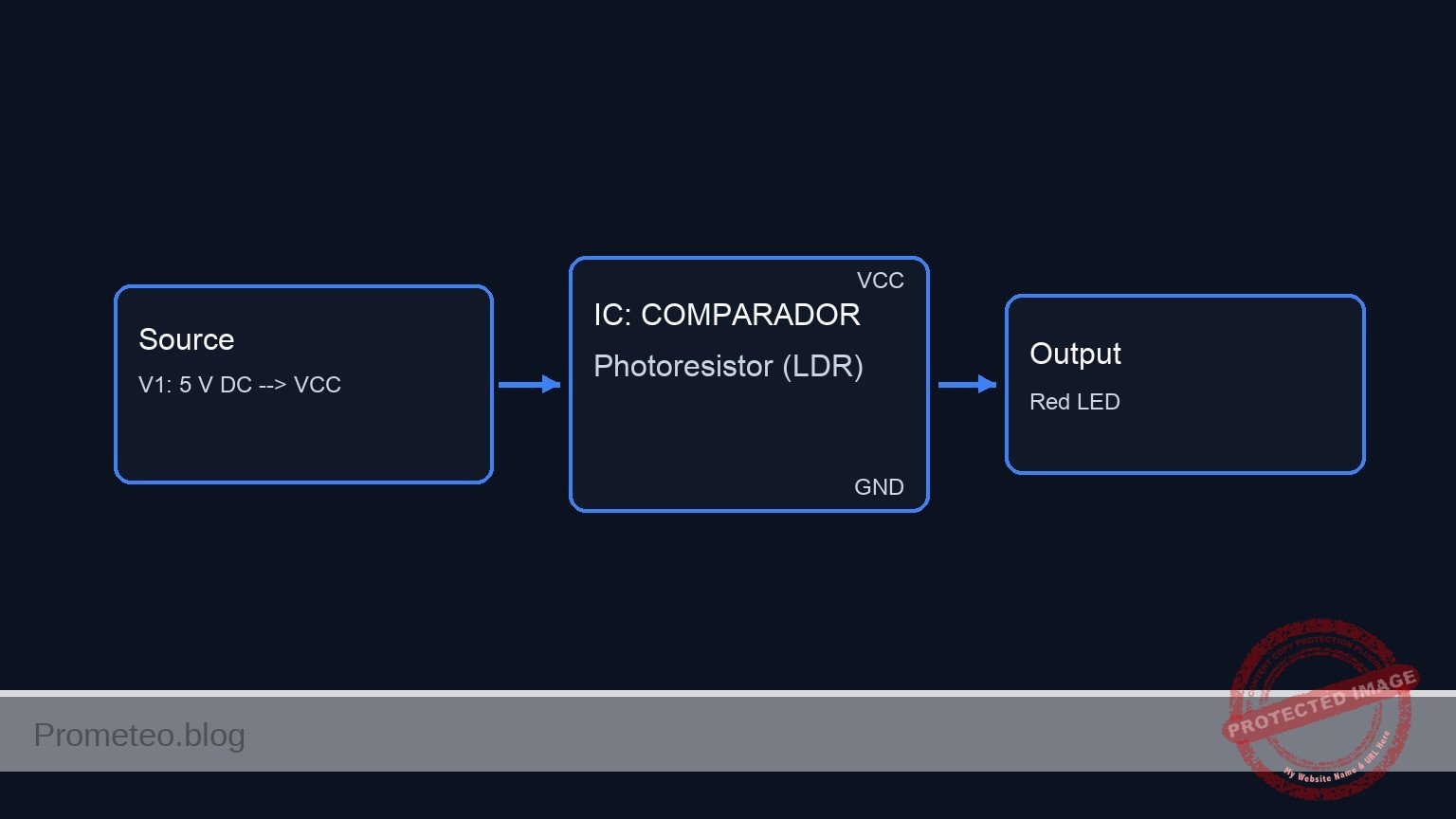

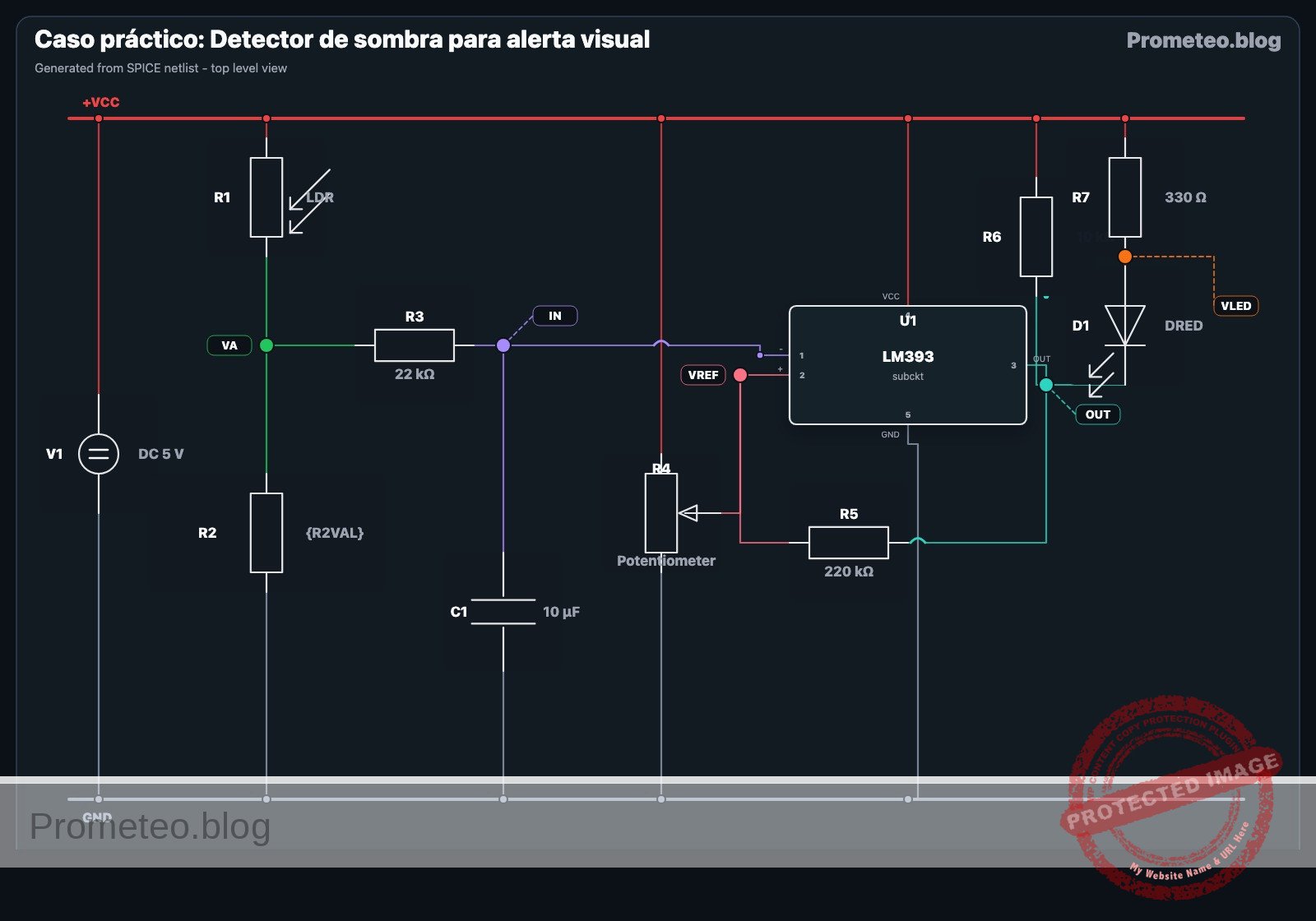

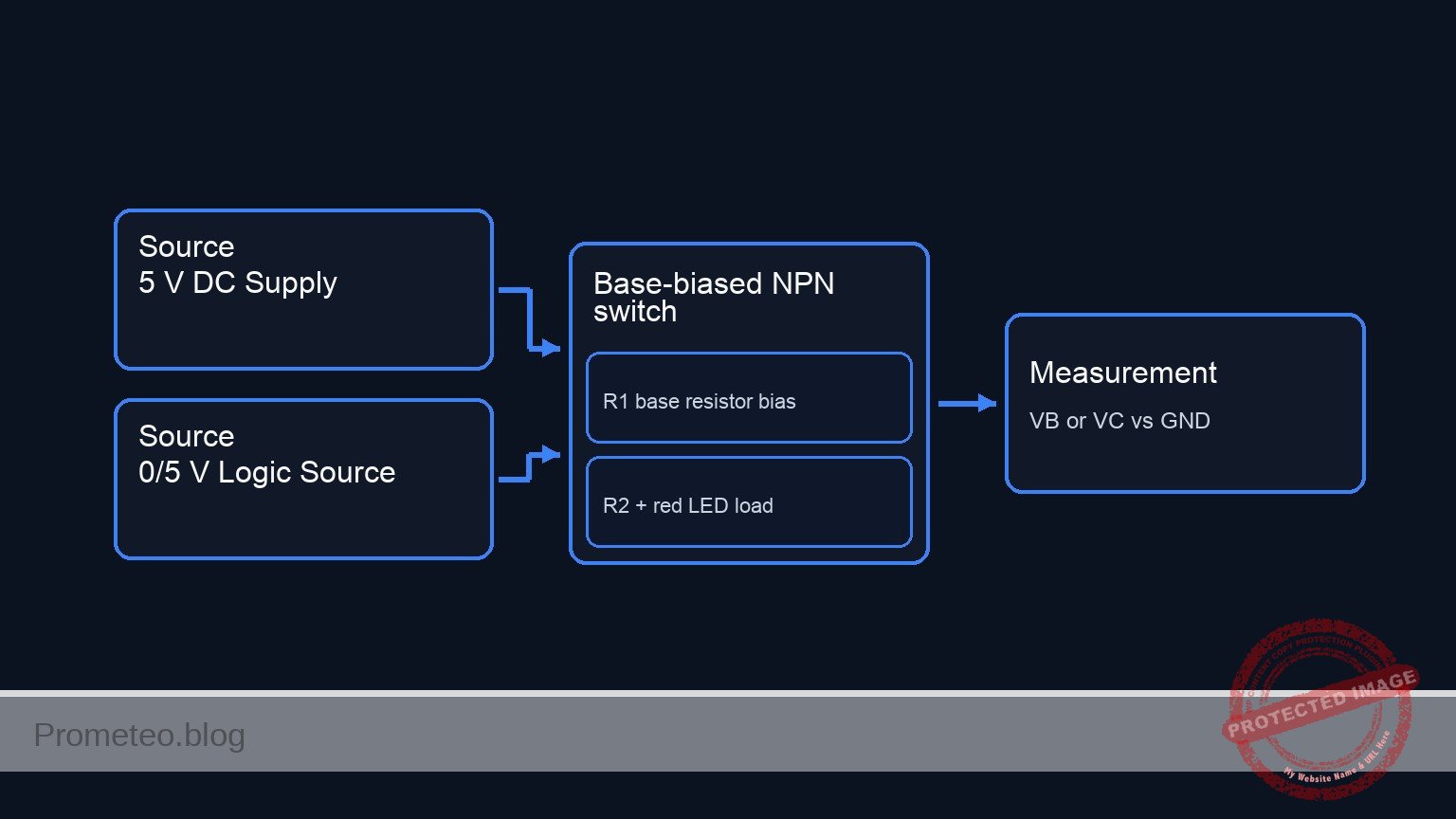

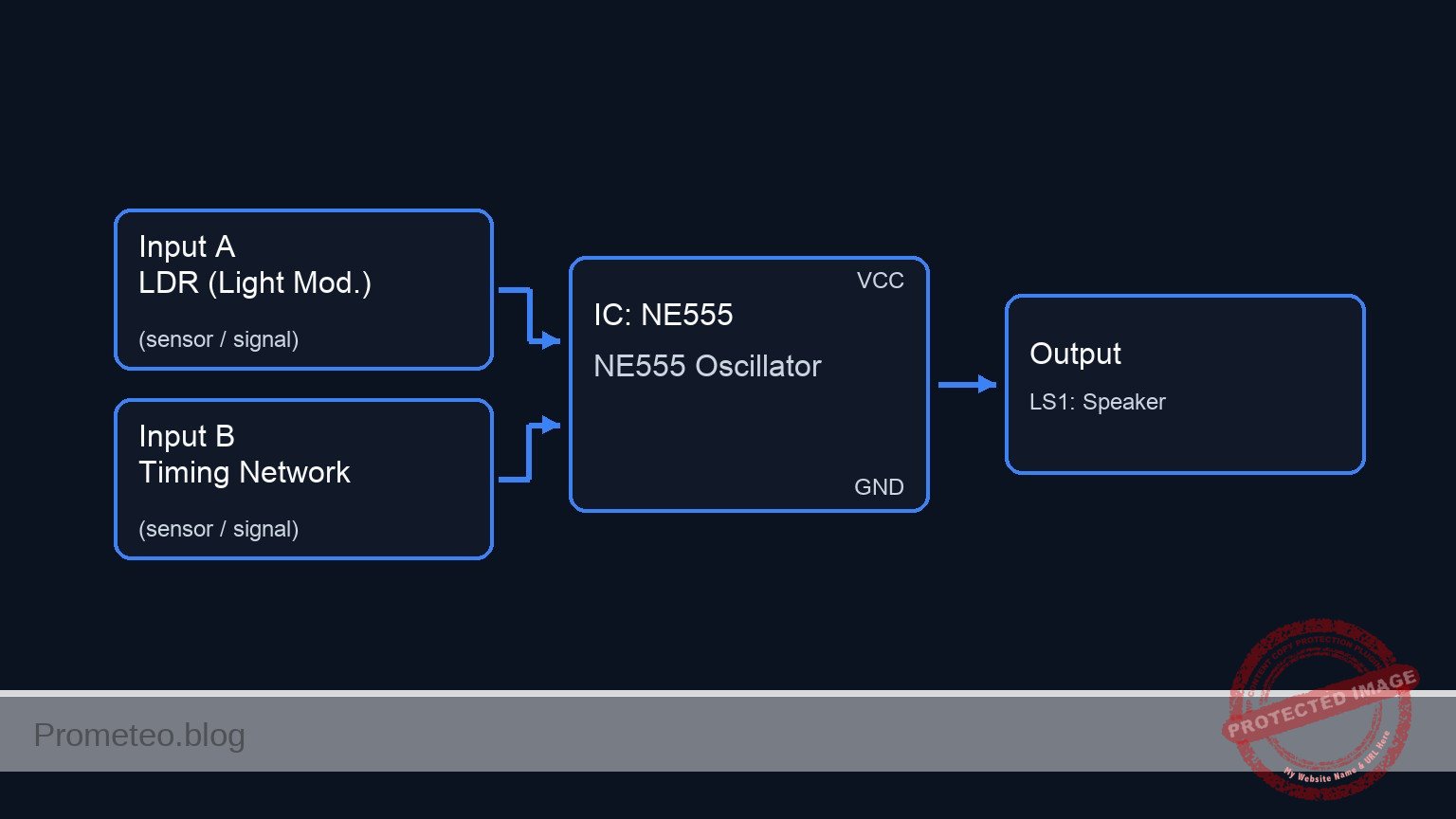

Diagrama de bloques conceptual

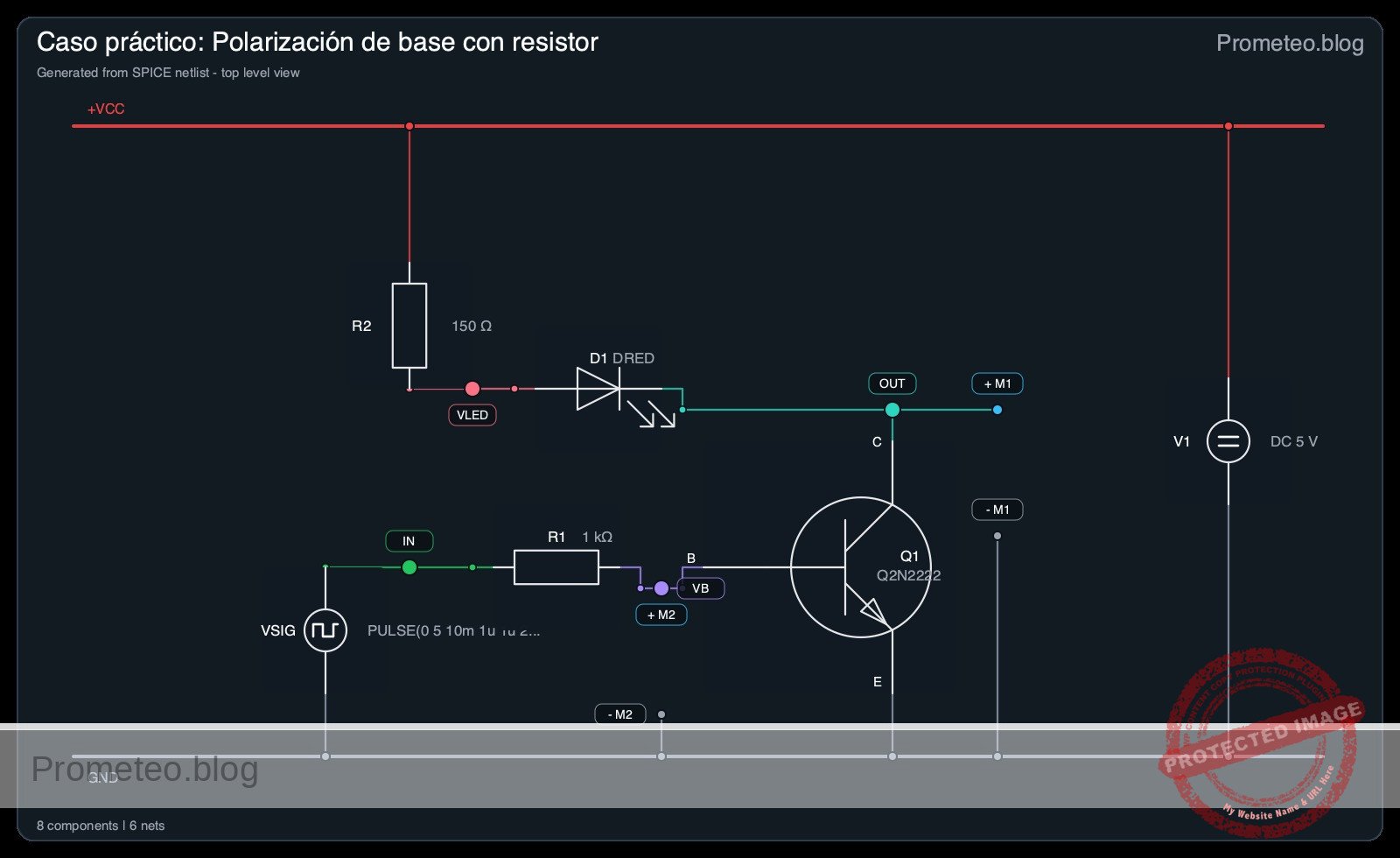

Esquemático

Inputs / Timing Network Processing Output / Load

======================= ========== =============

[ VCC --> R1: 1 kΩ ] -----------------------(DISCH: Pin 7)----> [ U1: NE555 Timer ]

[ ]

[ Node DISCH --> R2: LDR (Light Mod.) ] ---(TRIG_THR: Pins 2,6)[ ]

[ (Oscillator) ] --(OUT: Pin 3)--> [ C3: 10µF ] --(SPK_IN)--> [ LS1: Speaker ] --> GND

[ Node TRIG_THR --> C1: 100nF --> GND ] ---(Timing Ref)------> [ ]

[ ]

[ Node CTRL --> C2: 10nF --> GND ] --------(CTRL: Pin 5)-----> [ ]

Diagrama eléctrico

Mediciones y pruebas

- Resistencia de la LDR: Antes de insertar la LDR en el circuito, mide su resistencia con un multímetro digital. Registra el valor en oscuridad absoluta (debería ser muy alto, ej., > 50 kΩ) y bajo la iluminación directa de una linterna (debería disminuir significativamente, ej., < 1 kΩ).

- Voltaje del condensador: Alimenta el circuito ensamblado. Usa un osciloscopio para sondear el nodo

TRIG_THRcon respecto a tierra (nodo0). Deberías observar una forma de onda continua de carga y descarga (similar a una aleta de tiburón o un triángulo) oscilando exactamente entre 3 V y 6 V (que corresponden a 1/3 y 2/3 de la fuente de 9 V). - Frecuencia de salida: Conecta un osciloscopio o un frecuencímetro al nodo

OUTcon respecto a tierra. Ilumina directamente la LDR con una linterna y observa cómo la frecuencia aumenta rápidamente. Cubre el sensor con tu mano para simular la oscuridad y observa cómo la frecuencia cae.

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Light-controlled oscillator (NE555 astable)

.width out=256

.op

.tran 10u 5m uic

.print tran V(TRIG_THR) V(OUT) V(VCC) V(SPK_IN)

* Power Supply

V1 VCC 0 DC 9

* 555 Timer IC Subcircuit Definition

.subckt NE555 1 2 3 4 5 6 7 8

* Pins: 1:GND 2:TRIG 3:OUT 4:RESET 5:CTRL 6:THR 7:DISCH 8:VCC

* Internal voltage divider

R1 8 5 5k

R2 5 N_TRIG_REF 5k

R3 N_TRIG_REF 1 5k

* Comparators using continuous tanh functions for robust convergence

B_S N_S 1 V=0.5 + 0.5*tanh(100 * (V(N_TRIG_REF) - V(2)))

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Light-controlled oscillator (NE555 astable)

.width out=256

.op

.tran 10u 5m uic

.print tran V(TRIG_THR) V(OUT) V(VCC) V(SPK_IN)

* Power Supply

V1 VCC 0 DC 9

* 555 Timer IC Subcircuit Definition

.subckt NE555 1 2 3 4 5 6 7 8

* Pins: 1:GND 2:TRIG 3:OUT 4:RESET 5:CTRL 6:THR 7:DISCH 8:VCC

* Internal voltage divider

R1 8 5 5k

R2 5 N_TRIG_REF 5k

R3 N_TRIG_REF 1 5k

* Comparators using continuous tanh functions for robust convergence

B_S N_S 1 V=0.5 + 0.5*tanh(100 * (V(N_TRIG_REF) - V(2)))

B_R N_R 1 V=0.5 + 0.5*tanh(100 * (V(6) - V(5)))

B_RESET N_RESET 1 V=0.5 + 0.5*tanh(100 * (0.7 - (V(4) - V(1))))

* SR Latch (Behavioral RC model ensuring smooth transitions)

B_INT N_INT 1 V=(V(N_RESET)<=0.5) * ( (V(N_S)>=0.5) + (V(N_S)<0.5) * (V(N_R)<=0.5) * V(N_INT_CAP) )

R_INT N_INT N_INT_CAP 100

C_INT N_INT_CAP 1 1n

* Output stage (Push-pull behavior)

B_OUT N_OUT 1 V=(V(N_INT_CAP)>0.5) * V(8)

R_OUT N_OUT 3 10

* Discharge stage (Open collector behavior)

B_DISCH 7 1 I=V(7) * ( (V(N_INT_CAP)<0.5)*0.1 + (V(N_INT_CAP)>=0.5)*1e-9 )

.ends

* Main Circuit

XU1 0 TRIG_THR OUT VCC CTRL TRIG_THR DISCH VCC NE555

R1 VCC DISCH 1k

R2 DISCH TRIG_THR 10k

C1 TRIG_THR 0 100n

C2 CTRL 0 10n

C3 OUT SPK_IN 10u

RLS1 SPK_IN 0 1k

.end

* --- GPT review (BOM/Wiring/SPICE) ---

* circuit_ok=true

* simulation_summary: The transient simulation shows the trigger/threshold voltage oscillating between approximately 3V (1/3 VCC) and 6V (2/3 VCC), and the output toggling between near 0V and near 9V. The AC-coupled speaker input (SPK_IN) correctly centers around 0V during operation.

* bom_vs_spice equivalences ignored:

* - Photoresistor (LDR) R2 modeled as a fixed 10k resistor.

* - Piezoelectric speaker LS1 modeled as a 1k resistor RLS1.

* overall_comment: The SPICE netlist accurately represents the light-controlled oscillator described in the BOM and wiring guide. The NE555 subcircuit functions correctly as an astable multivibrator, and the simulation results confirm the expected oscillation. The circuit is perfectly suitable as a didactic example.

* --------------------------------------Resultados de Simulación (Transitorio)

Show raw data table (631 rows)

Index time v(trig_thr) v(out) v(vcc) v(spk_in) 0 1.000000e-07 8.901188e-06 0.000000e+00 9.000000e+00 0.000000e+00 1 1.014392e-07 2.067642e-05 8.910891e+00 9.000000e+00 8.910890e+00 2 1.043176e-07 4.422687e-05 8.910891e+00 9.000000e+00 8.910887e+00 3 1.100744e-07 9.132756e-05 8.910891e+00 9.000000e+00 8.910882e+00 4 1.215880e-07 1.855282e-04 8.910891e+00 9.000000e+00 8.910872e+00 5 1.446152e-07 3.739266e-04 8.910891e+00 9.000000e+00 8.910852e+00 6 1.906696e-07 7.507115e-04 8.910892e+00 9.000000e+00 8.910811e+00 7 2.827784e-07 1.504234e-03 8.910893e+00 9.000000e+00 8.910730e+00 8 4.361485e-07 2.758782e-03 8.910894e+00 9.000000e+00 8.910595e+00 9 6.136134e-07 4.210203e-03 8.910896e+00 9.000000e+00 8.910438e+00 10 8.824756e-07 6.408686e-03 8.910898e+00 9.000000e+00 8.910201e+00 11 1.315870e-06 9.951414e-03 8.910902e+00 9.000000e+00 8.909818e+00 12 2.182659e-06 1.703268e-02 8.910909e+00 9.000000e+00 8.909054e+00 13 3.916236e-06 3.117850e-02 8.910925e+00 9.000000e+00 8.907525e+00 14 7.383392e-06 5.940335e-02 8.910955e+00 9.000000e+00 8.904468e+00 15 1.000000e-05 8.064538e-02 8.910978e+00 9.000000e+00 8.902161e+00 16 1.069343e-05 8.626452e-02 8.910985e+00 9.000000e+00 8.901550e+00 17 1.208029e-05 9.749572e-02 8.910997e+00 9.000000e+00 8.900328e+00 18 1.485402e-05 1.199157e-01 8.911021e+00 9.000000e+00 8.897884e+00 19 2.040147e-05 1.645865e-01 8.911070e+00 9.000000e+00 8.892998e+00 20 3.040147e-05 2.445449e-01 8.911158e+00 9.000000e+00 8.884197e+00 21 4.040147e-05 3.237797e-01 8.911246e+00 9.000000e+00 8.875405e+00 22 5.040147e-05 4.022975e-01 8.911334e+00 9.000000e+00 8.866622e+00 23 6.040147e-05 4.801047e-01 8.911422e+00 9.000000e+00 8.857848e+00 ... (607 more rows) ...

Errores comunes y cómo evitarlos

- Intercambiar las posiciones de R1 y la LDR: Si la LDR se coloca entre VCC y el pin 7 (DISCHARGE), la luz intensa reducirá su resistencia a casi cero. Cuando el NE555 intente descargar el condensador conectando el pin 7 a tierra, creará un casi cortocircuito desde VCC hasta tierra, lo que podría destruir el CI. Mantén siempre una resistencia de seguridad fija (R1) en la posición superior.

- Elegir el valor incorrecto para C1: Si C1 es demasiado grande (como un condensador electrolítico de 10 µF), el oscilador funcionará a una frecuencia sub-audio, produciendo una serie de clics en lugar de un tono. Mantente en el rango de 10 nF a 100 nF para obtener resultados audibles.

- Omitir el condensador de acoplamiento de CA (C3): Conectar el altavoz piezoeléctrico directamente desde el pin de salida a tierra fuerza un desplazamiento de CC constante a través del altavoz, lo que consume energía innecesaria y puede degradar el componente con el tiempo. Utiliza siempre un condensador de acoplamiento de CA para bloquear la componente de CC.

Solución de problemas

- Síntoma: El altavoz emite un sonido de chasquido o tictac continuo en lugar de un tono musical.

- Causa: La frecuencia de oscilación es demasiado baja, probablemente por debajo de 20 Hz.

- Solución: Comprueba el valor de C1. Asegúrate de que es un condensador cerámico de 100 nF (a menudo marcado como 104) y no un condensador electrolítico mucho más grande. Además, asegúrate de que la LDR no esté en oscuridad total.

- Síntoma: No se produce ningún sonido y el chip NE555 se siente caliente al tacto.

- Causa: Un cortocircuito durante el ciclo de descarga.

- Solución: Desconecta la alimentación inmediatamente. Verifica que R1 sea una resistencia fija de 1 kΩ y que la LDR esté colocada estrictamente entre los pines 7 y 6, NO entre VCC y el pin 7.

- Síntoma: Se escucha un tono, pero el tono apenas cambia al pasar la mano sobre el sensor.

- Causa: La variación de resistencia de la LDR en las condiciones de iluminación actuales es demasiado pequeña, o la luz ambiental de la habitación es demasiado uniforme.

- Solución: Prueba el circuito iluminando la LDR directamente con una fuente de luz muy enfocada (como la linterna de un smartphone), y luego cúbrela completamente con un vaso oscuro. Si el tono sigue sin cambiar mucho, verifica que R2 sea efectivamente una LDR y no una resistencia fija estándar por error.

Posibles mejoras y extensiones

- Potenciómetro de sintonización manual: Añade un potenciómetro de 10 kΩ en serie con la LDR. Esto te permite compensar manualmente la resistencia total, proporcionando una forma de ajustar el «tono base» del oscilador para diferentes condiciones de iluminación de la habitación.

- Respuesta a la luz inversa: Modifica la configuración para que el tono disminuya a medida que aumenta la luz. Esto se puede lograr recableando la sección de temporización (teniendo en cuenta las resistencias de seguridad) o usando un transistor secundario para invertir el comportamiento de la LDR sobre el voltaje de control (Pin 5) del NE555 en lugar de la red de temporización estándar.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.