Nivel: Medio | Utiliza un condensador para mitigar el ruido mecánico al accionar un interruptor físico.

Objetivo y caso de uso

En este caso práctico, construirás una red RC pasiva (resistencia-condensador) conectada a un interruptor mecánico para filtrar los picos de voltaje de alta frecuencia generados por el rebote de los contactos.

Por qué es útil:

* Prevenir múltiples falsos disparos en contadores digitales o secuencias de pasos.

* Asegurar señales de interrupción limpias y únicas para microcontroladores.

* Estabilizar las lecturas de entrada para elementos de memoria como flip-flops y latches.

* Crear botones de interfaz de usuario fiables y predecibles en sistemas embebidos.

Resultado esperado:

* El rebote mecánico, que normalmente dura entre 1 y 5 ms, es absorbido completamente por el condensador.

* El voltaje en el nodo del interruptor realiza una transición suave en lugar de oscilar entre niveles lógicos.

* La constante de tiempo de carga define una curva de voltaje transitorio limpia al soltar el botón.

* Las mediciones con osciloscopio confirmarán la eliminación del tiempo de rebote en milisegundos.

Público objetivo y nivel: Estudiantes de electrónica de nivel intermedio y aficionados que aprenden sobre señales transitorias y características físicas de los interruptores.

Materiales

V1: Fuente de alimentación de 5 V CCSW1: Pulsador momentáneo SPST, función: disparador de entradaR1: Resistencia de 10 kΩ, función: pull-up para VSWC1: Condensador de 1 µF, función: suavizado antirrebote en paralelo al interruptor

Guía de conexionado

V1: se conecta entre el nodoVCCy el nodo0(GND).R1: se conecta entre el nodoVCCy el nodoVSW.SW1: se conecta entre el nodoVSWy el nodo0.C1: se conecta entre el nodoVSWy el nodo0.

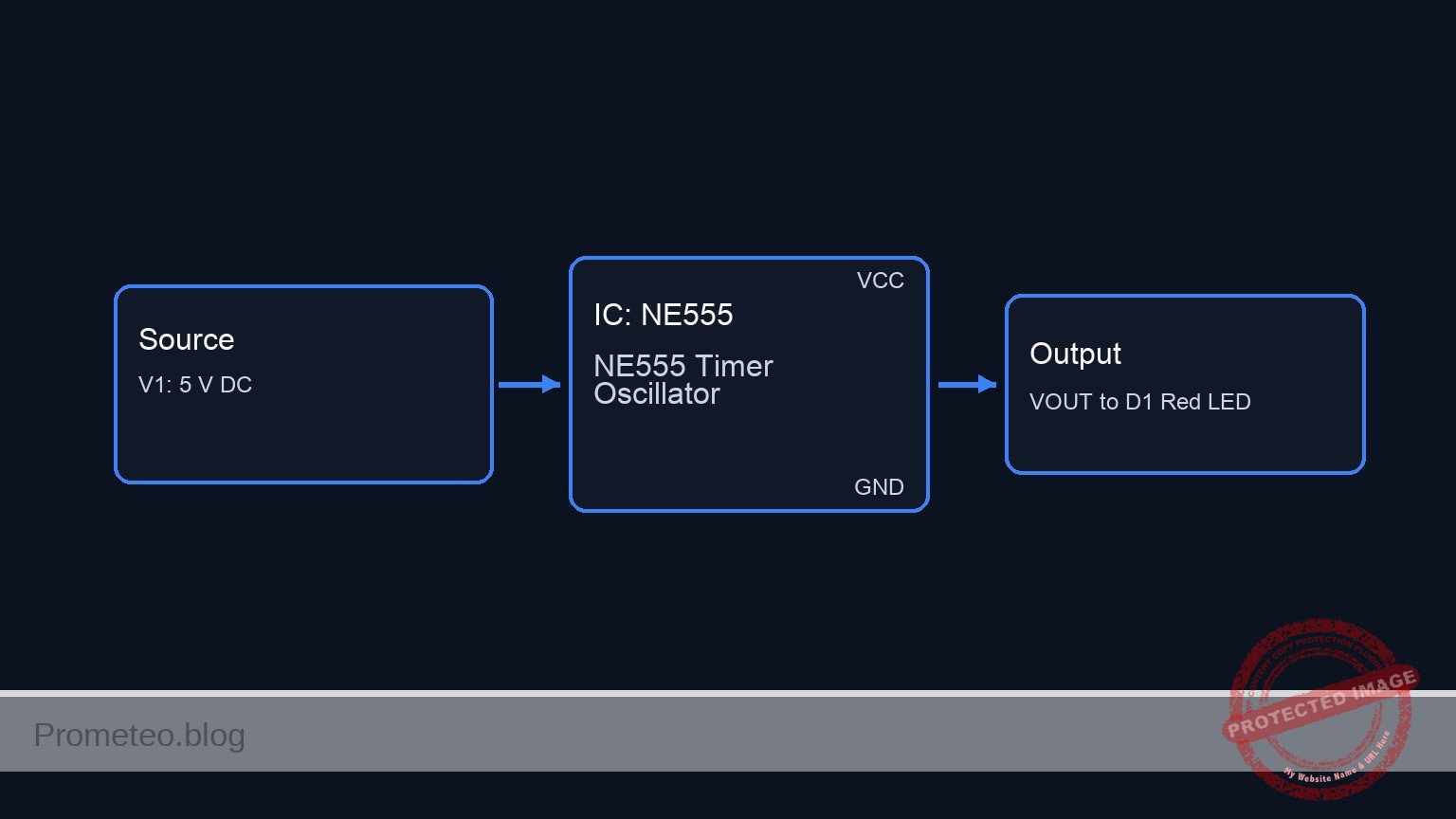

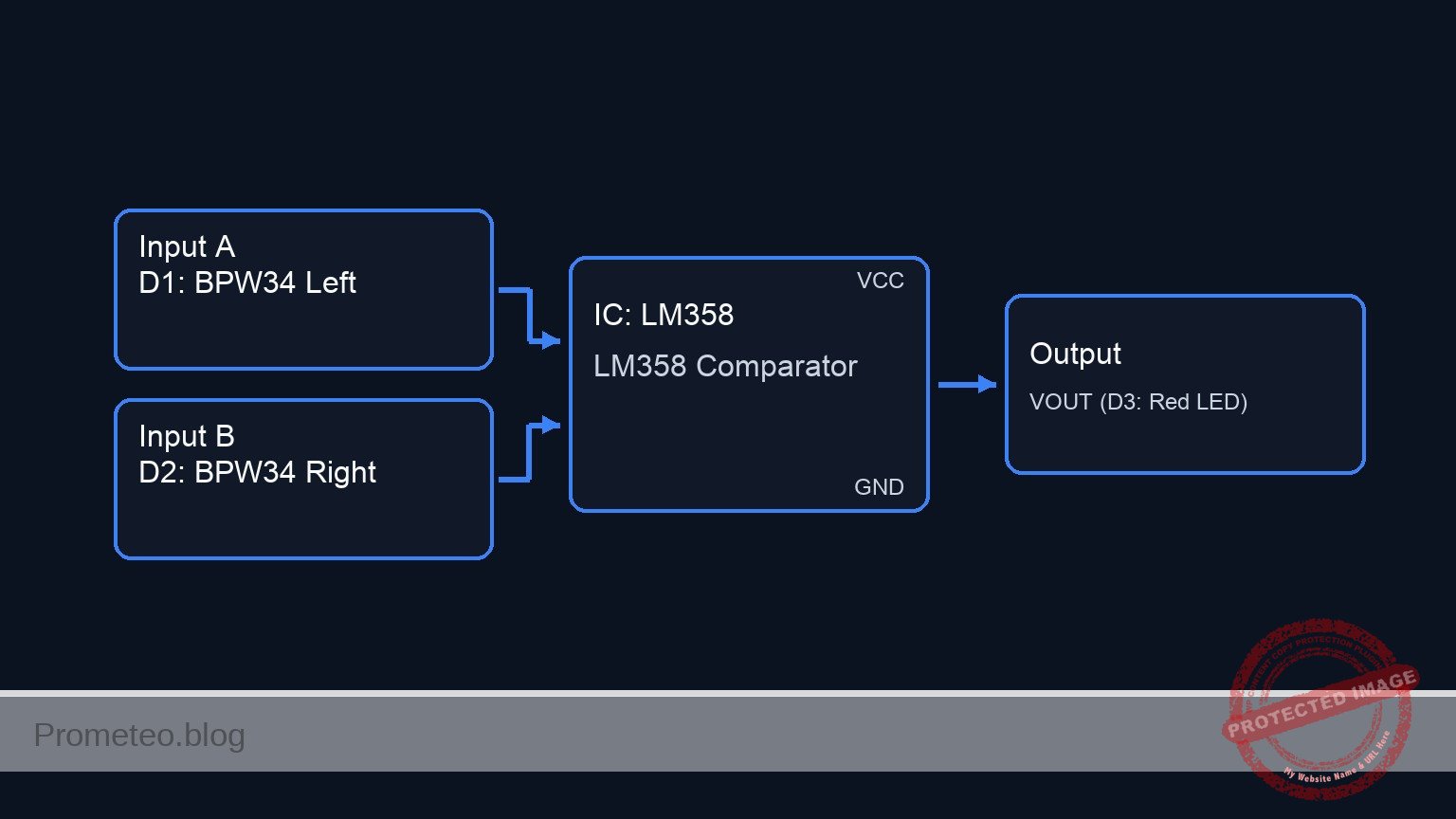

Diagrama de bloques conceptual

Esquemático

VCC (5 V) --> [ R1: 10 kΩ Pull-up ] --+--(Node VSW)--> [ Debounced Output ]

|

+--> [ SW1: Pushbutton ] --> GND

|

+--> [ C1: 1µF Capacitor ] --> GND

Mediciones y pruebas

- Conecta una sonda de osciloscopio al nodo

VSWy la pinza de tierra al nodo0. - Configura el osciloscopio para que se dispare en un flanco de bajada con un umbral de aproximadamente 2.5 V. Ajusta la base de tiempo a 2 ms/div para capturar con precisión el tiempo de rebote en ms (Bounce-Time-ms).

- Acciona

SW1(presiona el botón) y observa el voltaje transitorio (Transient-Voltage) en la pantalla. El voltaje debería caer a 0 V suavemente sin los picos rápidos característicos del rebote mecánico. - Suelta el interruptor y observa el flanco de subida. Mide el tiempo que tarda el voltaje en alcanzar 3.15 V (aprox. el 63.2% de 5 V). Esto representa una constante de tiempo RC (\tau = R × C), que teóricamente debería ser de 10 ms.

- Retira temporalmente

C1del circuito, presiona el interruptor nuevamente y observa el rebote mecánico en bruto para comparar las señales transitorias del antes y el después. Vuelve a insertarC1una vez completado.

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Practical case: RC pushbutton debounce

.width out=256

* Main DC Power Supply

V1 VCC 0 DC 5

* Pull-up Resistor

R1 VCC VSW 10k

* Debounce Smoothing Capacitor

C1 VSW 0 1u

* Pushbutton SW1 modeled as a voltage-controlled switch

* Connects VSW to 0 (GND) when the control voltage is high

S1 VSW 0 ctrl 0 switch_model

.model switch_model SW(Vt=2.5 Ron=1 Roff=100Meg)

* Control pulse simulating the user pressing the button

* Presses the button at 5ms, holds for 20ms, repeats every 50ms

Vctrl ctrl 0 PULSE(0 5 5m 1u 1u 20m 50m)

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Practical case: RC pushbutton debounce

.width out=256

* Main DC Power Supply

V1 VCC 0 DC 5

* Pull-up Resistor

R1 VCC VSW 10k

* Debounce Smoothing Capacitor

C1 VSW 0 1u

* Pushbutton SW1 modeled as a voltage-controlled switch

* Connects VSW to 0 (GND) when the control voltage is high

S1 VSW 0 ctrl 0 switch_model

.model switch_model SW(Vt=2.5 Ron=1 Roff=100Meg)

* Control pulse simulating the user pressing the button

* Presses the button at 5ms, holds for 20ms, repeats every 50ms

Vctrl ctrl 0 PULSE(0 5 5m 1u 1u 20m 50m)

* Analysis directives

.op

.tran 100u 100m

* CRITICAL: Print input (button press) and output (debounced signal)

.print tran V(ctrl) V(VSW)

.endResultados de Simulación (Transitorio)

Show raw data table (1134 rows)

Index time v(ctrl) v(vsw) 0 0.000000e+00 0.000000e+00 4.999500e+00 1 1.000000e-06 0.000000e+00 4.999500e+00 2 2.000000e-06 0.000000e+00 4.999500e+00 3 4.000000e-06 0.000000e+00 4.999500e+00 4 8.000000e-06 0.000000e+00 4.999500e+00 5 1.600000e-05 0.000000e+00 4.999500e+00 6 3.200000e-05 0.000000e+00 4.999500e+00 7 6.400000e-05 0.000000e+00 4.999500e+00 8 1.280000e-04 0.000000e+00 4.999500e+00 9 2.280000e-04 0.000000e+00 4.999500e+00 10 3.280000e-04 0.000000e+00 4.999500e+00 11 4.280000e-04 0.000000e+00 4.999500e+00 12 5.280000e-04 0.000000e+00 4.999500e+00 13 6.280000e-04 0.000000e+00 4.999500e+00 14 7.280000e-04 0.000000e+00 4.999500e+00 15 8.280000e-04 0.000000e+00 4.999500e+00 16 9.280000e-04 0.000000e+00 4.999500e+00 17 1.028000e-03 0.000000e+00 4.999500e+00 18 1.128000e-03 0.000000e+00 4.999500e+00 19 1.228000e-03 0.000000e+00 4.999500e+00 20 1.328000e-03 0.000000e+00 4.999500e+00 21 1.428000e-03 0.000000e+00 4.999500e+00 22 1.528000e-03 0.000000e+00 4.999500e+00 23 1.628000e-03 0.000000e+00 4.999500e+00 ... (1110 more rows) ...

Errores comunes y cómo evitarlos

- Elegir un valor de condensador demasiado grande: Usar un condensador de 100 µF con una resistencia pull-up de 10 kΩ da como resultado una constante de tiempo de 1 segundo, lo que provoca una respuesta lenta del botón. Solución: Mantén

C1entre 100 nF y 1 µF para resistencias pull-up estándar de 10 kΩ. - Omitir la resistencia pull-up: Sin

R1, el nodoVSWflotará de manera impredecible cuando el interruptor esté abierto. Solución: Asegúrate siempre de queR1esté conectada de forma segura entreVCCy el nodo del interruptor. - Alimentar la señal lenta RC directamente en lógica digital estándar: Las puertas lógicas estándar (como un 74HC08 básico) pueden oscilar si se alimentan con un voltaje de subida lenta. Solución: Usa este circuito para comprender el transitorio RC, pero para entradas digitales reales, pasa la señal sin rebotes a través de un CI Schmitt Trigger para cuadrar los flancos.

Solución de problemas

- Síntoma: El voltaje en el nodo

VSWse mantiene constantemente en 0 V. - Causa: El interruptor está atascado físicamente cerrado, o el condensador

C1está en cortocircuito. - Solución: Verifica la continuidad del interruptor con un multímetro y reemplaza

C1si está defectuoso. - Síntoma: El voltaje en el nodo

VSWse mantiene constantemente en 5 V incluso al presionarlo. - Causa:

SW1no está conectado correctamente al nodo0(Tierra). - Solución: Verifica la conexión a tierra en el terminal inferior del interruptor.

- Síntoma: El rebote del interruptor aún es visible en el flanco de subida.

- Causa: La constante de tiempo RC es demasiado corta en comparación con la duración del rebote mecánico de ese interruptor en específico.

- Solución: Aumenta el valor de

C1(por ejemplo, de 0.1 µF a 1 µF). - Síntoma: Los contactos del interruptor fallan o se degradan después de pulsaciones repetidas.

- Causa: El condensador descarga su carga instantáneamente a través de los contactos del interruptor, causando una alta corriente de irrupción (inrush current).

- Solución: Para una fiabilidad a largo plazo, añade una pequeña resistencia de 100 Ω en serie con el interruptor para limitar la corriente de descarga.

Posibles mejoras y extensiones

- Añadir un buffer Schmitt Trigger: Pasa el nodo

VSWa través de un inversor Schmitt Trigger (como el 74HC14) para convertir la curva de carga exponencial RC en un pulso lógico digital nítido y sin rebotes. - Comparación de antirrebote por Hardware vs Software: Mantén este circuito RC por hardware en un botón, y conecta un botón en bruto (sin circuito) a un microcontrolador. Implementa un algoritmo de antirrebote por software en el botón en bruto y compara el uso de recursos y la fiabilidad de ambos métodos.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.