Nivel: Básico – Verificar la relación de división de frecuencia en las salidas Q de un contador binario con respecto al reloj.

Objetivo y caso de uso

En este caso práctico, construirá un circuito digital utilizando un contador binario de 4 bits (74HC393) para dividir la frecuencia de una señal de reloj de entrada por factores de 2 (2^1), 4 (2^2) y 8 (2^3).

- Relojes digitales: Se utilizan para dividir señales de osciladores de cristal de alta frecuencia hasta 1 Hz para mantener el tiempo (segundos).

- Síntesis de audio: Se utiliza para generar octavas más bajas a partir de un tono base (la reducción de la frecuencia a la mitad da como resultado un tono una octava más bajo).

- Generación de velocidad de baudios: Se utiliza en la comunicación UART para derivar velocidades de transmisión de datos específicas a partir de un reloj maestro del sistema.

- Contadores de direcciones: Se utilizan para secuenciar direcciones de memoria en microcontroladores.

Resultado esperado:

* Salida Q0: Una onda cuadrada con una frecuencia exactamente la mitad del reloj de entrada (f/2).

* Salida Q1: Una onda cuadrada con una frecuencia de un cuarto del reloj de entrada (f/4).

* Salida Q2: Una onda cuadrada con una frecuencia de un octavo del reloj de entrada (f/8).

* Público objetivo: Estudiantes de nivel básico y aficionados.

Materiales

- V1: Fuente de alimentación de 5 V CC, función: Fuente de alimentación principal.

- V_CLK: Generador de pulsos (0 V a 5 V, 1 kHz, ciclo de trabajo del 50%), función: Señal de reloj de entrada.

- U1: 74HC393, función: Contador binario dual de 4 bits.

- R1: Resistencia de 330 Ω, función: Limitación de corriente para el LED D1.

- R2: Resistencia de 330 Ω, función: Limitación de corriente para el LED D2.

- R3: Resistencia de 330 Ω, función: Limitación de corriente para el LED D3.

- D1: LED rojo, función: Indicador visual para Q0 (f/2).

- D2: LED verde, función: Indicador visual para Q1 (f/4).

- D3: LED amarillo, función: Indicador visual para Q2 (f/8).

- Scope: Osciloscopio de 4 canales, función: Análisis de formas de onda.

Pin-out del CI utilizado

Chip seleccionado: 74HC393 (Contador binario dual de 4 bits). Usaremos el primer bloque contador (Lado 1).

| Pin | Nombre | Función lógica | Conexión en este caso |

|---|---|---|---|

| 1 | 1CP (CLK) | Entrada de reloj (Disparo por flanco de bajada) | Conectado a CLK_IN |

| 2 | 1MR | Reset maestro (Activo en alto) | Conectado a 0 (GND) |

| 3 | 1Q0 | Salida Bit 0 (Divide por 2) | Conectado a Q0 |

| 4 | 1Q1 | Salida Bit 1 (Divide por 4) | Conectado a Q1 |

| 5 | 1Q2 | Salida Bit 2 (Divide por 8) | Conectado a Q2 |

| 7 | GND | Tierra | Conectado a 0 |

| 14 | VCC | Alimentación (+5 V) | Conectado a VCC |

Guía de conexionado

- V1 se conecta entre el nodo

VCCy el nodo0(GND). - U1 pin 14 se conecta al nodo

VCC. - U1 pin 7 se conecta al nodo

0(GND). - U1 pin 2 (Reset) se conecta al nodo

0(GND) para habilitar el conteo. - V_CLK se conecta entre el nodo

CLK_INy el nodo0(GND). - U1 pin 1 se conecta al nodo

CLK_IN. - U1 pin 3 se conecta al nodo

Q0. - U1 pin 4 se conecta al nodo

Q1. - U1 pin 5 se conecta al nodo

Q2. - R1 se conecta entre el nodo

Q0y el nodoLED_Q0. - D1 el ánodo se conecta a

LED_Q0, el cátodo se conecta a0(GND). - R2 se conecta entre el nodo

Q1y el nodoLED_Q1. - D2 el ánodo se conecta a

LED_Q1, el cátodo se conecta a0(GND). - R3 se conecta entre el nodo

Q2y el nodoLED_Q2. - D3 el ánodo se conecta a

LED_Q2, el cátodo se conecta a0(GND).

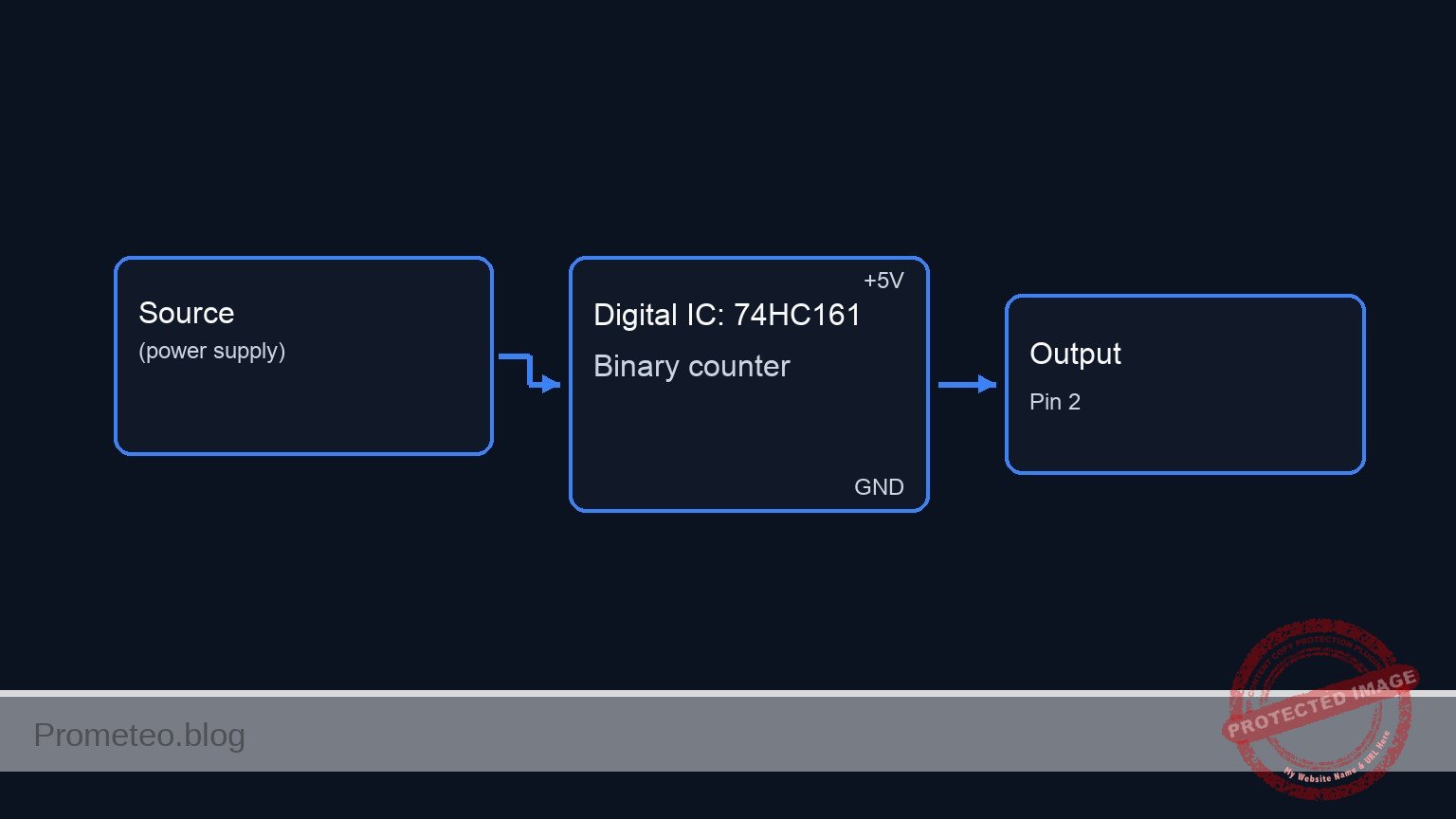

Diagrama de bloques conceptual

Esquemático

INPUTS PROCESSING OUTPUTS / LOADS

(Left) (Center) (Right)

+-----------------------+

| |

[ V_CLK: 1kHz ] --(Pin 1: CP)---> | | --(Pin 3: Q0)--> [ R1: 330 ] --> [ D1: Red ] --> GND

| | |

| U1: 74HC393 | '--------(Scope Ch1: f/2)

| Dual 4-bit |

| Bin Counter |

[ GND ] ---------(Pin 2: MR)---> | | --(Pin 4: Q1)--> [ R2: 330 ] --> [ D2: Grn ] --> GND

(Reset Disabled) | (Power: VCC=Pin 14, | |

| GND=Pin 7) | '--------(Scope Ch2: f/4)

| |

| |

| | --(Pin 5: Q2)--> [ R3: 330 ] --> [ D3: Yel ] --> GND

| | |

+-----------------------+ '--------(Scope Ch3: f/8)

Mediciones y pruebas

Para validar el circuito, realice las siguientes mediciones utilizando el osciloscopio de 4 canales:

- Configuración: Conecte la pinza de tierra de todas las sondas del osciloscopio al nodo

0(GND). - Canal 1 (Entrada): Conecte a

CLK_IN. Verifique que la frecuencia sea de 1 kHz. - Canal 2 (Q0): Conecte a

Q0. Mida la frecuencia. Debe ser 500 Hz ($1kHz / 2$). - Canal 3 (Q1): Conecte a

Q1. Mida la frecuencia. Debe ser 250 Hz ($1kHz / 4$). - Canal 4 (Q2): Conecte a

Q2. Mida la frecuencia. Debe ser 125 Hz ($1kHz / 8$). - Comprobación visual: Si reduce la frecuencia del reloj de entrada a 10 Hz, debería ver a D1 parpadear más rápido, D2 más lento y D3 el más lento.

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Practical case: Frequency divider by 2, 4 and 8

.width out=256

* --- Models ---

* Generic LED Model

.model DLED D(IS=1e-14 N=2 RS=10 BV=5 IBV=10u CJO=10p)

* --- Power Supply ---

* V1: 5V Main Supply

V1 VCC 0 DC 5

* --- Input Signal ---

* V_CLK: 1kHz Pulse, 0V to 5V, 50% Duty Cycle

V_CLK CLK_IN 0 PULSE(0 5 0 1u 1u 0.5m 1m)

* --- Subcircuit: 74HC393 (Behavioral XSPICE) ---

* Dual 4-bit Binary Counter

* Implements Counter 1 logic using XSPICE primitives.

* Pinout (DIP-14): 1=1CP, 2=1MR, 3=1Q0, 4=1Q1, 5=1Q2, 6=1Q3, 7=GND

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Practical case: Frequency divider by 2, 4 and 8

.width out=256

* --- Models ---

* Generic LED Model

.model DLED D(IS=1e-14 N=2 RS=10 BV=5 IBV=10u CJO=10p)

* --- Power Supply ---

* V1: 5V Main Supply

V1 VCC 0 DC 5

* --- Input Signal ---

* V_CLK: 1kHz Pulse, 0V to 5V, 50% Duty Cycle

V_CLK CLK_IN 0 PULSE(0 5 0 1u 1u 0.5m 1m)

* --- Subcircuit: 74HC393 (Behavioral XSPICE) ---

* Dual 4-bit Binary Counter

* Implements Counter 1 logic using XSPICE primitives.

* Pinout (DIP-14): 1=1CP, 2=1MR, 3=1Q0, 4=1Q1, 5=1Q2, 6=1Q3, 7=GND

* 8=2Q3, 9=2Q2, 10=2Q1, 11=2Q0, 12=2MR, 13=2CP, 14=VCC

.subckt 74HC393 1CP 1MR 1Q0 1Q1 1Q2 1Q3 GND 2Q3 2Q2 2Q1 2Q0 2MR 2CP VCC

* ADC Bridge to read analog inputs (Clock and Reset)

.model adc_mod adc_bridge(in_low=1.5 in_high=3.5)

A_IN [1CP 1MR] [d_1cp d_1mr] adc_mod

* ADC Bridge to read GND for Logic Low (used for SET inputs)

A_GND [GND] [d_low] adc_mod

* Logic Models

.model inv_mod d_inverter(rise_delay=10n fall_delay=10n)

.model dff_mod d_dff(clk_delay=10n rise_delay=10n fall_delay=10n)

.model dac_mod dac_bridge(out_low=0.0 out_high=5.0)

* --- Counter Logic (Side 1) ---

* 74HC393 triggers on High-to-Low transition of CP.

* XSPICE DFF triggers on Rising Edge. So we invert CP.

A_INV1 d_1cp d_1cp_inv inv_mod

* Stage 1 (Q0): Divider by 2

* T-FF behavior: D = ~Q. Clock = ~CP. Reset = MR.

* Port order: din clk set reset out nout

A_DFF1 d_1q0_bar d_1cp_inv d_low d_1mr d_1q0 d_1q0_bar dff_mod

* Stage 2 (Q1): Divider by 4

* Ripples from Q0 Falling Edge.

* Q0 Falling = ~Q0 Rising. Use d_1q0_bar as clock.

A_DFF2 d_1q1_bar d_1q0_bar d_low d_1mr d_1q1 d_1q1_bar dff_mod

* Stage 3 (Q2): Divider by 8

* Ripples from Q1 Falling Edge. Use d_1q1_bar as clock.

A_DFF3 d_1q2_bar d_1q1_bar d_low d_1mr d_1q2 d_1q2_bar dff_mod

* Stage 4 (Q3): Divider by 16 (Not used externally but part of logic)

A_DFF4 d_1q3_bar d_1q2_bar d_low d_1mr d_1q3 d_1q3_bar dff_mod

* Drive Outputs

A_OUT [d_1q0 d_1q1 d_1q2 d_1q3] [1Q0 1Q1 1Q2 1Q3] dac_mod

* Side 2 is unused, inputs grounded in main circuit, outputs open.

.ends 74HC393

* --- Main Circuit Instances ---

* U1: 74HC393 Counter

* Pin connections based on Wiring Guide:

* 1(CLK_IN), 2(0/Reset), 3(Q0), 4(Q1), 5(Q2), 7(0/GND), 14(VCC)

* Unused outputs mapped to NC nodes. Unused inputs to 0.

* Subcircuit Pin Order: 1CP 1MR 1Q0 1Q1 1Q2 1Q3 GND 2Q3 2Q2 2Q1 2Q0 2MR 2CP VCC

XU1 CLK_IN 0 Q0 Q1 Q2 NC_1Q3 0 NC_2Q3 NC_2Q2 NC_2Q1 NC_2Q0 0 0 VCC 74HC393

* --- Output Paths (LEDs and Resistors) ---

* Path 1: Q0 -> R1 -> D1 (Red)

R1 Q0 LED_Q0 330

D1 LED_Q0 0 DLED

* Path 2: Q1 -> R2 -> D2 (Green)

R2 Q1 LED_Q1 330

D2 LED_Q1 0 DLED

* Path 3: Q2 -> R3 -> D3 (Yellow)

R3 Q2 LED_Q2 330

D3 LED_Q2 0 DLED

* --- Simulation & Output ---

.op

.tran 10u 20m

.print tran V(CLK_IN) V(Q0) V(Q1) V(Q2)

.end

* --- GPT review (BOM/Wiring/SPICE) ---

* circuit_ok=true

* simulation_summary: The simulation shows a clear binary counting sequence. CLK_IN is a 1kHz clock (period 1ms). Q0 toggles every 1ms (f/2, period 2ms). Q1 toggles every 2ms (f/4, period 4ms). Q2 toggles every 4ms (f/8, period 8ms). The outputs transition cleanly between 0V and 5V.

* bom_vs_spice equivalences ignored:

* - LEDs (D1, D2, D3) are modeled using a generic diode model (DLED) with specific parameters.

* - U1 (74HC393) is modeled as a behavioral subcircuit using XSPICE primitives (ADC/DAC bridges, DFFs) instead of a transistor-level model.

* overall_comment: The circuit is perfectly functional and accurately represents a 3-bit binary ripple counter (frequency divider). The behavioral model for the 74HC393 is correctly implemented with the necessary ADC/DAC bridges for XSPICE. The wiring matches the guide exactly, and the simulation results confirm the expected frequency division ratios (f/2, f/4, f/8). It is an excellent didactic example.

* --------------------------------------Resultados de Simulación (Transitorio)

Show raw data table (3323 rows)

Index time v(clk_in) v(q0) v(q1) v(q2) 0 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 1 1.000000e-08 5.000000e-02 0.000000e+00 0.000000e+00 0.000000e+00 2 2.000000e-08 1.000000e-01 0.000000e+00 0.000000e+00 0.000000e+00 3 4.000000e-08 2.000000e-01 0.000000e+00 0.000000e+00 0.000000e+00 4 8.000000e-08 4.000000e-01 0.000000e+00 0.000000e+00 0.000000e+00 5 1.600000e-07 8.000000e-01 0.000000e+00 0.000000e+00 0.000000e+00 6 3.200000e-07 1.600000e+00 0.000000e+00 0.000000e+00 0.000000e+00 7 6.400000e-07 3.200000e+00 0.000000e+00 0.000000e+00 0.000000e+00 8 1.000000e-06 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 9 1.064000e-06 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 10 1.192000e-06 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 11 1.448000e-06 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 12 1.960000e-06 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 13 2.984000e-06 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 14 5.032000e-06 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 15 9.128000e-06 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 16 1.732000e-05 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 17 2.732000e-05 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 18 3.732000e-05 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 19 4.732000e-05 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 20 5.732000e-05 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 21 6.732000e-05 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 22 7.732000e-05 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 23 8.732000e-05 5.000000e+00 0.000000e+00 0.000000e+00 0.000000e+00 ... (3299 more rows) ...

Errores comunes y cómo evitarlos

- Dejar flotante el pin Master Reset (MR): Dejar el pin 2 desconectado provoca que el contador se reinicie aleatoriamente debido al ruido. Solución: Conecte siempre el pin MR a GND (Lógica 0) para un funcionamiento normal de conteo.

- Confundir los números de los pines: El 74HC393 tiene dos contadores en su interior. Los estudiantes a menudo mezclan los pines del Contador 1 y del Contador 2. Solución: Siga estrictamente la hoja de datos (datasheet) y utilice los pines 1, 2, 3, 4, 5 y 6 solo para el primer contador.

- Ignorar VCC/GND: Olvidar alimentar el chip conduce a una salida impredecible o sin actividad. Solución: Conecte siempre el Pin 14 a +5 V y el Pin 7 a GND antes de realizar pruebas.

Solución de problemas

- Síntoma: Ningún LED se enciende y las salidas permanecen en 0 V.

- Causa: El Master Reset (Pin 2) podría estar conectado a VCC en lugar de a GND.

- Solución: Mueva la conexión del Pin 2 a GND.

- Síntoma: Los LED están siempre encendidos o parpadean muy tenuemente.

- Causa: La frecuencia es demasiado alta para que el ojo vea el parpadeo (por ejemplo, 1 kHz).

- Solución: Utilice el osciloscopio para verificar la señal o reduzca la frecuencia de V_CLK a < 10 Hz para confirmación visual.

- Síntoma: La frecuencia de salida es inestable o errática.

- Causa: Fuente de alimentación ruidosa o falta de condensador de desacoplo.

- Solución: Añada un condensador de 100 nF entre VCC y GND cerca del CI.

Posibles mejoras y extensiones

- Dividir por 16 y 256: Conecte en cascada el primer contador al segundo contador del chip U1 (conecte 1Q3 a 2CP) para lograr relaciones de división más altas hasta 256.

- Generador de audio variable: Conecte las salidas a un controlador de altavoz simple y utilice un potenciómetro variable en un temporizador 555 (como reloj) para escuchar cómo el tono cae por octavas al cambiar entre Q0, Q1 y Q2.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.