Nivel: Básico. Analizando la inestabilidad causada por entradas incorrectas de divisores de tensión en puertas digitales.

Objetivo y caso de uso

En este caso práctico, construirás un circuito donde la entrada a un inversor digital (puerta NOT) se mantiene exactamente a 2.5 V usando un divisor de tensión simétrico. Esto crea un estado «prohibido» para las familias lógicas de 5 V.

- Entendiendo los umbrales lógicos: Aprende por qué las entradas digitales necesitan tensiones Alta y Baja definidas, no solo «algo en el medio».

- Diagnosticando la inestabilidad: Reconoce los síntomas de estados indefinidos, como la oscilación o el calentamiento excesivo.

- Comportamiento interno del transistor: Visualiza qué sucede con los MOSFETs internos cuando la tensión de entrada está en la «zona muerta».

Resultado esperado:

* Señal: La tensión de entrada (Vin) mide exactamente 2.5 V.

* Salida: El LED de salida puede estar tenue, parpadeando o atascado en una tensión intermedia (no totalmente 0 V o 5 V).

* Térmico: El chip 74HC04 puede calentarse ligeramente debido a la corriente interna de «shoot-through» (conducción cruzada).

Público objetivo: Estudiantes que trabajan con interfaces de sensores y niveles lógicos.

Materiales

- V1: Fuente de alimentación de 5 V DC, función: Fuente de alimentación principal

- R1: Resistencia de 10 kΩ, función: Rama superior del divisor de tensión

- R2: Resistencia de 10 kΩ, función: Rama inferior del divisor de tensión

- U1: 74HC04, función: Hex Inverter (puerta NOT)

- R3: Resistencia de 330 Ω, función: Limitación de corriente del LED

- D1: LED rojo, función: Indicador de estado lógico

- C1: Condensador de 100 nF, función: Desacoplo de la fuente de alimentación

Pin-out del CI utilizado

Chip: 74HC04 (Hex Inverter)

| Pin | Nombre | Función lógica | Conexión en este caso |

|---|---|---|---|

| 1 | 1 A | Entrada | Conectado al divisor de tensión (2.5 V) |

| 2 | 1Y | Salida | Conectado a la resistencia del LED |

| 7 | GND | Tierra | Conectado a Tierra de la fuente de alimentación |

| 14 | VCC | Alimentación (+5 V) | Conectado a +5 V de la fuente de alimentación |

Guía de conexionado

- VCC: Conecta el terminal positivo de V1, el Pin 14 de U1 y un lado de R1.

- 0 (GND): Conecta el terminal negativo de V1, el Pin 7 de U1, un lado de R2 y el cátodo (patilla corta) de D1.

- V_IN: Conecta el lado restante de R1, el lado restante de R2 y el Pin 1 (Entrada 1 A) de U1. Nota: Este nodo crea el nivel problemático de 2.5 V.

- V_OUT: Conecta el Pin 2 (Salida 1Y) de U1 a un lado de R3.

- LED_NODE: Conecta el lado restante de R3 al ánodo (patilla larga) de D1.

- Desacoplo: Conecta C1 directamente entre el Pin 14 y el Pin 7 de U1.

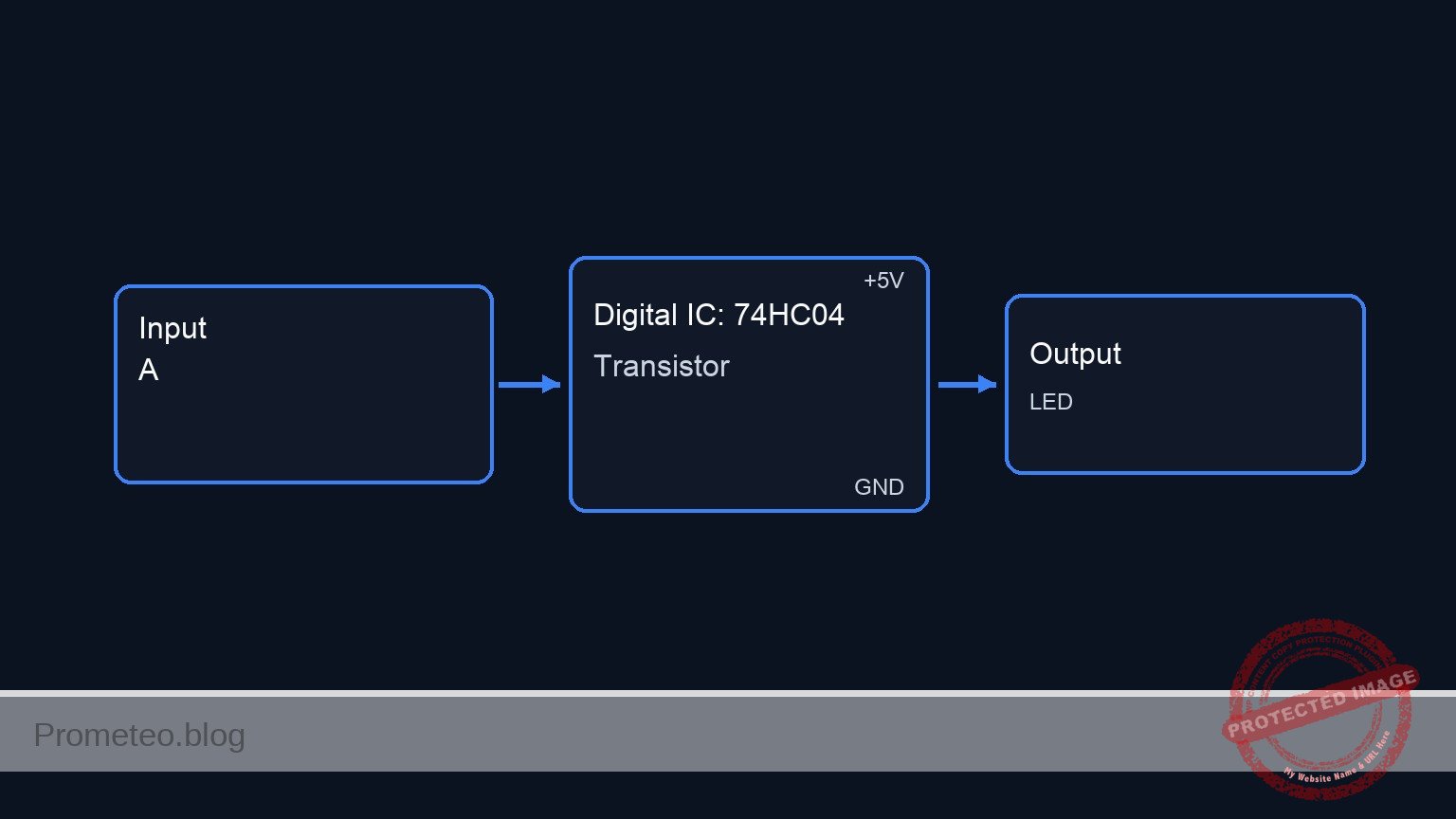

Diagrama de bloques conceptual

Esquemático

INPUT STAGE (Voltage Divider) PROCESSING STAGE (Logic) OUTPUT STAGE (Load) VCC (5 V) | [ R1: 10 kΩ ] | +---------(V_IN: ~2.5 V)---------> [ U1: 74HC04 (Inverter) ] -------(V_OUT)-------> [ R3: 330 Ω ] ----> [ D1: LED ] ----> GND | (Undefined Level) [ Input: Pin 1 ] [ R2: 10 kΩ ] [ Output: Pin 2 ] | [ Power: VCC/GND + C1 ] GND (0 V)

Tabla de verdad

Puerta: NOT (Inversor)

| Entrada (A) | Salida (Y) |

|---|---|

| L (0 V) | H (5 V) |

| H (5 V) | L (0 V) |

| 2.5 V | Indefinido / Inestable |

Mediciones y pruebas

- Comprobación de tensión de entrada: Configura tu multímetro en tensión continua (DC). Coloca la sonda roja en el nodo V_IN (Pin 1 de U1) y la sonda negra en GND. Verifica que la lectura sea de aproximadamente 2.5 V.

- Observación de la salida: Mira D1. Podría estar brillando tenuemente o parpadeando. Esto indica que la salida no está proporcionando un nivel lógico Alto o Bajo sólido.

- Comprobación de tensión de salida: Mide la tensión en V_OUT (Pin 2). Probablemente no será 0 V ni 5 V, sino un valor intermedio, o puede estar oscilando (lectura fluctuante).

- Prueba táctil (Precaución): Toca con cuidado la parte superior del encapsulado de plástico del 74HC04. Si el chip se siente más caliente que la temperatura ambiente, está consumiendo corriente en exceso.

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Practical case: The Undefined Logic Level Danger

.width out=256

* --- Models ---

* Generic Red LED Model

.model LED_RED D(IS=1e-22 N=1.5 RS=10 BV=5 CJO=50p IBV=1u)

* Subcircuit for U1: 74HC04 Hex Inverter

* Pinout: 1=Input(A), 2=Output(Y), 7=GND, 14=VCC

* Implemented with a continuous sigmoid function to allow robust simulation

* of the linear region (undefined state) without convergence issues.

.subckt 74HC04 1 2 7 14

B_INV 2 7 V = V(14,7) / (1 + exp(20 * (V(1,7) - 0.5*V(14,7))))

.ends

* --- Components ---

* V1: Main Power Supply

* Using PULSE to simulate power-on transient (0V to 5V)

V1 VCC 0 PULSE(0 5 1u 10u 10u 100m 200m)

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Practical case: The Undefined Logic Level Danger

.width out=256

* --- Models ---

* Generic Red LED Model

.model LED_RED D(IS=1e-22 N=1.5 RS=10 BV=5 CJO=50p IBV=1u)

* Subcircuit for U1: 74HC04 Hex Inverter

* Pinout: 1=Input(A), 2=Output(Y), 7=GND, 14=VCC

* Implemented with a continuous sigmoid function to allow robust simulation

* of the linear region (undefined state) without convergence issues.

.subckt 74HC04 1 2 7 14

B_INV 2 7 V = V(14,7) / (1 + exp(20 * (V(1,7) - 0.5*V(14,7))))

.ends

* --- Components ---

* V1: Main Power Supply

* Using PULSE to simulate power-on transient (0V to 5V)

V1 VCC 0 PULSE(0 5 1u 10u 10u 100m 200m)

* R1: Top leg of voltage divider (10k)

R1 VCC V_IN 10k

* R2: Bottom leg of voltage divider (10k)

* This creates approx 2.5V at V_IN when VCC is 5V

R2 V_IN 0 10k

* U1: 74HC04 Hex Inverter

* Connections: Pin 1=V_IN, Pin 2=V_OUT, Pin 7=0(GND), Pin 14=VCC

XU1 V_IN V_OUT 0 VCC 74HC04

* C1: Decoupling capacitor (100nF)

C1 VCC 0 100n

* R3: LED current limiting resistor (330 Ohm)

R3 V_OUT LED_NODE 330

* D1: Red LED

D1 LED_NODE 0 LED_RED

* --- Analysis ---

* Transient analysis to capture power-up and settling

* Step size 1us, Stop time 500us

.tran 1u 500u

* Print directives for simulation logging

.print tran V(V_IN) V(V_OUT) V(LED_NODE) V(VCC)

* Operating point calculation

.op

.endResultados de Simulación (Transitorio)

Show raw data table (519 rows)

Index time v(v_in) v(v_out) v(led_node) v(vcc) 0 0.000000e+00 0.000000e+00 0.000000e+00 -1.32954e-36 0.000000e+00 1 1.000000e-08 0.000000e+00 0.000000e+00 -8.37118e-37 0.000000e+00 2 2.000000e-08 0.000000e+00 0.000000e+00 -2.17031e-37 0.000000e+00 3 4.000000e-08 0.000000e+00 0.000000e+00 6.442019e-37 0.000000e+00 4 8.000000e-08 0.000000e+00 0.000000e+00 1.087387e-36 0.000000e+00 5 1.600000e-07 0.000000e+00 0.000000e+00 5.886649e-37 0.000000e+00 6 3.200000e-07 0.000000e+00 0.000000e+00 -7.16419e-38 0.000000e+00 7 6.400000e-07 0.000000e+00 0.000000e+00 -1.33719e-37 0.000000e+00 8 1.000000e-06 0.000000e+00 0.000000e+00 -1.75658e-38 0.000000e+00 9 1.005123e-06 1.280776e-03 1.280776e-03 3.255392e-04 2.561552e-03 10 1.015369e-06 3.842328e-03 3.842328e-03 1.418765e-03 7.684656e-03 11 1.035862e-06 8.965432e-03 8.965432e-03 5.258943e-03 1.793086e-02 12 1.070382e-06 1.759552e-02 1.759552e-02 1.345000e-02 3.519104e-02 13 1.105069e-06 2.626716e-02 2.626716e-02 2.210557e-02 5.253431e-02 14 1.174442e-06 4.361042e-02 4.361042e-02 3.941132e-02 8.722085e-02 15 1.313188e-06 7.829696e-02 7.829696e-02 7.402122e-02 1.565939e-01 16 1.590680e-06 1.476700e-01 1.476700e-01 1.432281e-01 2.953401e-01 17 2.145665e-06 2.864162e-01 2.864162e-01 2.815810e-01 5.728324e-01 18 3.145665e-06 5.364162e-01 5.364162e-01 5.305352e-01 1.072832e+00 19 4.145665e-06 7.864162e-01 7.864162e-01 7.789169e-01 1.572832e+00 20 5.145665e-06 1.036416e+00 1.036416e+00 1.027633e+00 2.072832e+00 21 6.145665e-06 1.286416e+00 1.286416e+00 1.276050e+00 2.572832e+00 22 7.145665e-06 1.536416e+00 1.536416e+00 1.521539e+00 3.072832e+00 23 8.145665e-06 1.786416e+00 1.786416e+00 1.662480e+00 3.572832e+00 ... (495 more rows) ...

Errores comunes y cómo evitarlos

- Asumir que 2.5 V es «Alto»: Muchos estudiantes piensan que cualquier tensión > 0 V es «Alta». Consulta la hoja de datos para los requisitos mínimos de VIH (Tensión de entrada Alta) (generalmente ~3.5 V para lógica HC de 5 V).

- Usar divisores de alta impedancia: Usar 10 kΩ/10 kΩ está bien para referencias, pero el ruido puede acoplarse fácilmente en este nodo de alta impedancia, causando que la puerta conmute aleatoriamente.

- Ignorar los condensadores de desacoplo: En este estado inestable, el chip genera ruido en los rieles de alimentación. Omitir C1 hace que el comportamiento sea aún más errático.

Solución de problemas

- Síntoma: El LED está tenue o parpadea rápidamente.

- Causa: La entrada está en la «región lineal» o «zona prohibida». Los transistores internos están amplificando ruido.

- Solución: Ajusta la tensión de entrada para que sea claramente válida (p. ej., conecta la Entrada directamente a VCC o GND para probar).

- Síntoma: El chip se está calentando, pero el LED funciona.

- Causa: Corriente de «shoot-through». Dentro del chip, tanto el P-MOSFET como el N-MOSFET de la etapa de entrada están conduciendo parcialmente porque 2.5 V los polariza a ambos en ON. Esto crea un cortocircuito desde VCC a GND dentro del silicio.

- Solución: Nunca dejes una entrada CMOS en una tensión intermedia.

- Síntoma: La tensión en V_IN no es exactamente 2.5 V.

- Causa: Tolerancia de las resistencias (p. ej., resistencias del 5% o 10%) o carga del multímetro.

- Solución: Mide los valores de R1 y R2 independientemente o verifica con un multímetro de precisión.

🕵️ Ver Diagnóstico y Solución (Clic para revelar)

### Diagnóstico y Solución

**1. El Problema (Síntoma):** «El LED parpadea, está tenue o el chip se calienta. La entrada mide 2.5 V. ¿Es eso un 1 o un 0?»

**2. La Investigación:** Mides Vin y confirmas que es 2.5 V. Consultas la hoja de datos del 74HC04:

* VIL (Entrada Baja Máx) = 1.35 V

* VIH (Entrada Alta Mín) = 3.15 V

* **Resultado:** ¡Estás en «Tierra de Nadie»! La tensión es mayor que un Bajo, pero menor que un Alto.

**3. La Revelación:** Esto demuestra los **Márgenes de Ruido** y la Física de Transistores. A 2.5 V, tanto los transistores internos de entrada PMOS como NMOS están parcialmente encendidos (ON). Esto crea un camino directo para que fluya corriente desde VCC a GND (Shoot-through), causando calor. La salida se vuelve impredecible y sensible incluso a milivoltios de ruido.

**4. La Solución:** Modifica el divisor para entregar un nivel lógico seguro.

* **Para enviar un ‘1’:** Cambia **R1 a 1 kΩ** (y mantén R2 en 10k). Vout ≈ 4.5 V (Alto Lógico Sólido).

* **Para enviar un ‘0’:** Cambia **R2 a 1 kΩ** (y mantén R1 en 10k). Vout ≈ 0.45 V (Bajo Lógico Sólido).

Posibles mejoras y extensiones

- Implementación de histéresis: Reemplaza el 74HC04 con un 74HC14 (Inversor Schmitt Trigger). Observa cómo el Schmitt trigger maneja la entrada de 2.5 V (permanecerá en el estado anterior hasta que se cruce un umbral específico) sin oscilar.

- Entrada Variable: Reemplaza las resistencias fijas R1/R2 con un potenciómetro de 10 kΩ. Barre la tensión de 0 V a 5 V mientras mides la corriente de alimentación (Amperaje). Verás un pico de corriente exactamente alrededor del punto de transición de 2.5 V.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.