Nivel: Medio | Comprender el desplazamiento del nivel DC de una señal AC utilizando un diodo y un condensador.

Objetivo y caso de uso

Construirás un circuito fijador de nivel positivo con diodo que toma una señal AC entrante centrada en cero y desplaza todo su nivel DC hacia arriba, estableciendo una nueva línea base de referencia.

Este circuito es muy útil en diversas aplicaciones prácticas:

* Restaurar niveles DC en señales de video analógicas para una correcta representación en pantalla.

* Proteger las etapas de entrada analógica de microcontroladores que no pueden manejar voltajes negativos.

* Crear los bloques de construcción fundamentales para circuitos multiplicadores de voltaje (como las bombas de carga).

* Polarizar señales AC para que puedan ser procesadas por amplificadores operacionales de fuente simple.

Resultado esperado:

* La forma de onda AC de entrada (V_in_waveform) seguirá siendo una onda senoidal estándar centrada en 0 V.

* La forma de onda AC de salida (V_out_waveform) tendrá la misma amplitud pico a pico, pero estará desplazada por encima de 0 V.

* Se establecerá un DC_offset medible en la salida, aproximadamente igual al voltaje pico de entrada menos la caída de voltaje directo del diodo.

Público objetivo y nivel: Estudiantes de electrónica de nivel intermedio que aprenden sobre conformación de ondas y circuitos no lineales.

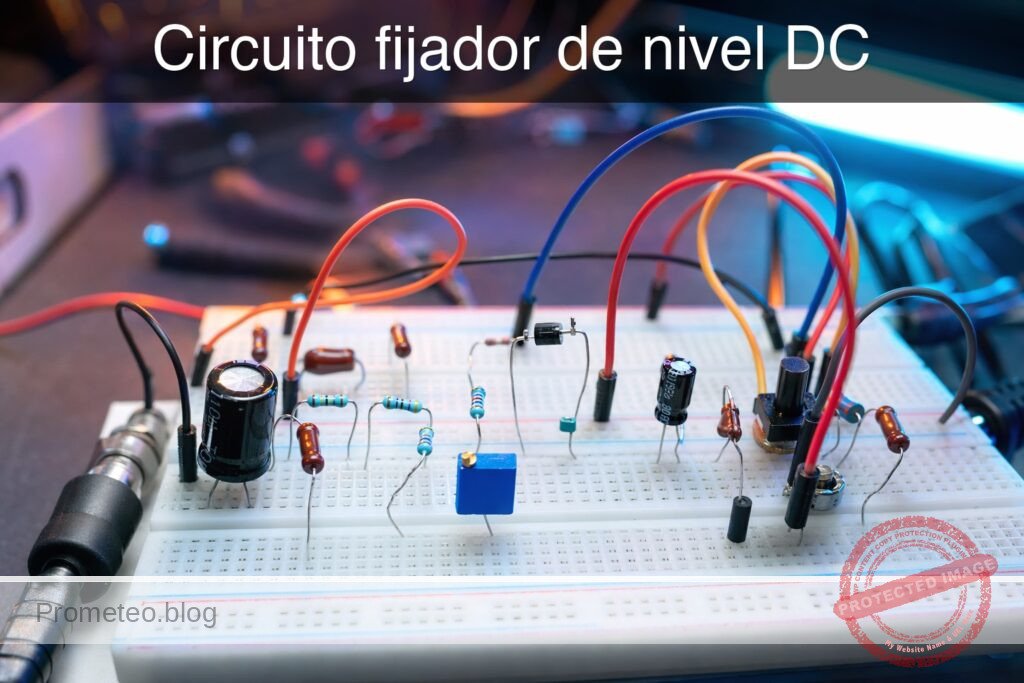

Materiales

V1: fuente de onda senoidal AC de 5 V pico (10 Vpp) a 1 kHz, función: señal de entradaC1: condensador de 1 µF, función: acoplamiento AC y almacenamiento del desplazamiento DCD1: diodo de pequeña señal 1N4148, función: fija el nivel de voltaje mínimoR1: resistencia de 100 kΩ, función: proporciona una ruta de descarga y define la carga

Guía de conexionado

V1: se conecta entre el nodoVIN(positivo) y el nodo0(GND).C1: se conecta entre el nodoVINy el nodoVOUT.D1: se conecta entre el nodo0(ánodo) y el nodoVOUT(cátodo).R1: se conecta entre el nodoVOUTy el nodo0(GND).

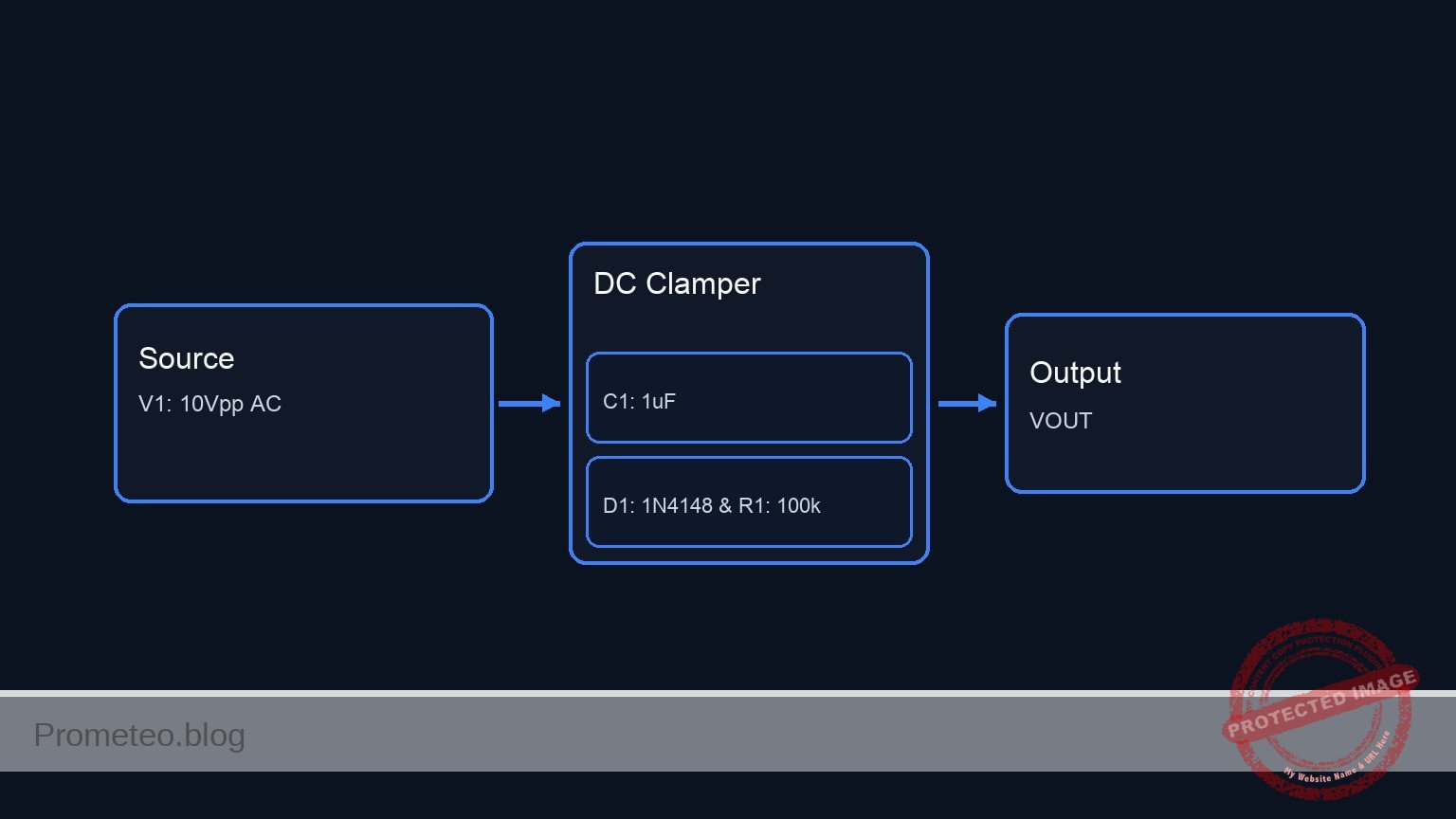

Diagrama de bloques conceptual

Esquemático

[ V1: 10Vpp AC ] --(VIN)--> [ C1: 1µF ] --(VOUT)--+--> [ R1: 100 kΩ ] --> GND

|

+--> [ D1: 1N4148 Cathode ] --(Anode)--> GND

Mediciones y pruebas

- Generación de señal: Conecta tu generador de funciones o fuente AC para proporcionar una onda senoidal de 10 Vpp a 1 kHz al nodo

VIN. - Verificación de entrada: Mide el nodo

VINcon un canal del osciloscopio (acoplamiento DC). Verifica que laV_in_waveformoscile simétricamente de -5 V a +5 V. - Forma de onda de salida: Mide el nodo

VOUTcon un segundo canal del osciloscopio (acoplamiento DC). Observa laV_out_waveform. Debería oscilar aproximadamente de -0.7 V a +9.3 V. - Medición del desplazamiento DC: Cambia tu multímetro digital (DMM) al modo de voltaje DC y mide el nodo

VOUTcon respecto al nodo0. Deberías leer unDC_offsetpositivo de aproximadamente +4.3 V. - Comprobación de la constante de tiempo: Nota cómo la forma de onda de salida mantiene su forma. El alto valor de

R1asegura que el condensador no se descargue significativamente entre ciclos.

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice)

* Practical case: DC level clamper circuit

.width out=256

* Input Signal: 5V peak (10Vpp), 1kHz sine wave

V1 VIN 0 SINE(0 5 1k)

* AC coupling and DC offset storage capacitor

C1 VIN VOUT 1u

* Clamping diode (Anode to GND, Cathode to VOUT)

D1 0 VOUT 1N4148

* Load resistor and discharge path

R1 VOUT 0 100k

* Standard 1N4148 diode model

.model 1N4148 D(IS=4.35E-9 N=1.906 BV=110 IBV=0.0001 RS=0.6458 CJO=1.20E-11 M=0.3333 VJ=0.75 TT=3.48E-9)

* Transient analysis for 5 milliseconds to capture 5 full cycles of the 1kHz signal

.tran 10u 5m

* Output directives (Input and Output nodes first)

.print tran V(VIN) V(VOUT)

.op

.endCopia este contenido en un archivo .cir y ejecútalo con ngspice.

Resultados de Simulación (Transitorio)

Show raw data table (509 rows)

Index time v(vin) v(vout) 0 0.000000e+00 0.000000e+00 -2.62072e-15 1 1.000000e-07 3.141592e-03 3.141552e-03 2 1.768596e-07 5.556208e-03 5.556134e-03 3 3.305789e-07 1.038543e-02 1.038529e-02 4 6.380174e-07 2.004385e-02 2.004355e-02 5 1.252894e-06 3.936043e-02 3.935972e-02 6 2.482649e-06 7.799154e-02 7.798965e-02 7 4.942157e-06 1.552375e-01 1.552318e-01 8 9.861173e-06 3.095997e-01 3.095809e-01 9 1.969921e-05 6.172898e-01 6.172223e-01 10 2.969921e-05 9.276226e-01 9.274748e-01 11 3.969921e-05 1.234294e+00 1.234036e+00 12 4.969921e-05 1.536095e+00 1.535695e+00 13 5.969921e-05 1.831833e+00 1.831263e+00 14 6.969921e-05 2.120342e+00 2.119572e+00 15 7.969921e-05 2.400483e+00 2.399485e+00 16 8.969921e-05 2.671151e+00 2.669897e+00 17 9.969921e-05 2.931276e+00 2.929740e+00 18 1.096992e-04 3.179833e+00 3.177990e+00 19 1.196992e-04 3.415841e+00 3.413667e+00 20 1.296992e-04 3.638368e+00 3.635840e+00 21 1.396992e-04 3.846536e+00 3.843632e+00 22 1.496992e-04 4.039523e+00 4.036224e+00 23 1.596992e-04 4.216569e+00 4.212856e+00 ... (485 more rows) ...

Errores comunes y cómo evitarlos

- Invertir la polaridad del diodo: Colocar el diodo con el cátodo hacia GND creará un fijador negativo en lugar de uno positivo. Verifica siempre la orientación de la banda negra (cátodo) en el diodo físico.

- Usar una resistencia de carga (R1) demasiado pequeña: Si

R1es demasiado pequeña, la constante de tiempo RC será más corta que el período de la señal, lo que hará que el condensador se descargue demasiado rápido y distorsione la forma de onda de salida hasta darle forma de «aleta de tiburón». - Usar un condensador polarizado incorrectamente: Si usas un condensador electrolítico para

C1, la pata positiva debe mirar hacia el lado con el voltaje DC promedio más alto (en este caso de fijador positivo, mirando hacia el nodoVOUT).

Solución de problemas

- Síntoma: La forma de onda de salida es idéntica a la forma de onda de entrada (centrada en 0 V).

- Causa: El diodo

D1está abierto, desconectado, o el condensadorC1está en cortocircuito. - Solución: Comprueba la continuidad del diodo con un multímetro y asegúrate de que el condensador esté conectado en serie con la señal.

- Causa: El diodo

- Síntoma: La forma de onda de salida es plana en 0 V o -0.7 V.

- Causa: El diodo

D1está en cortocircuito a tierra, oVOUTestá conectado accidentalmente de forma directa a GND. - Solución: Inspecciona el cableado de la protoboard en el nodo

VOUTy reemplaza el diodo si falla en una prueba en modo diodo.

- Causa: El diodo

- Síntoma: El nivel DC es correcto, pero la forma de onda tiene una caída o inclinación severa en los bordes planos.

- Causa: La constante de tiempo RC es demasiado baja para la frecuencia de 1 kHz.

- Solución: Aumenta el valor de

R1(por ejemplo, de 10 kΩ a 100 kΩ) o aumentaC1para evitar una descarga prematura.

Posibles mejoras y extensiones

- Fijador polarizado: Agrega una pequeña fuente de voltaje DC (por ejemplo, una batería de 1.5 V) en serie con el diodo

D1(entre el ánodo y GND) para fijar la señal a un nivel de referencia arbitrario distinto de -0.7 V. - Conversión a fijador negativo: Invierte la dirección de

D1(ánodo aVOUT, cátodo a0) y observa cómo toda la forma de onda AC se desplaza hacia abajo, situándose completamente por debajo de +0.7 V.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.