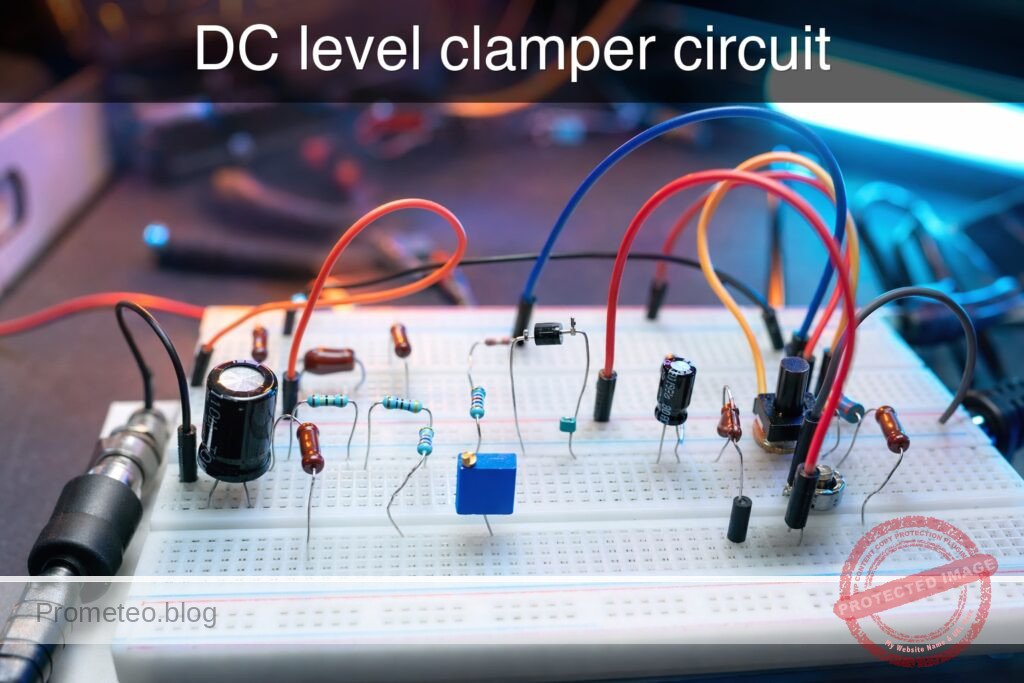

Level: Medium | Understand the shifting of the DC level of an AC signal using a diode and a capacitor.

Objective and use case

You will build a positive diode clamper circuit that takes an incoming zero-centered AC signal and shifts its entire DC level upwards, establishing a new reference baseline.

This circuit is highly useful in various practical applications:

* Restoring DC levels in analog video signals for proper display rendering.

* Protecting the analog input stages of microcontrollers that cannot handle negative voltages.

* Creating the foundational building blocks for voltage multiplier circuits (like charge pumps).

* Biasing AC signals so they can be processed by single-supply operational amplifiers.

Expected outcome:

* The input AC waveform (V_in_waveform) will remain a standard sine wave centered at 0 V.

* The output AC waveform (V_out_waveform) will have the same peak-to-peak amplitude but will be shifted above 0 V.

* A measurable DC_offset will be established at the output, roughly equal to the peak input voltage minus the diode’s forward voltage drop.

Target audience and level: Intermediate electronics students learning wave shaping and non-linear circuits.

Materials

V1: 5 V peak (10 Vpp) 1 kHz AC sine wave source, function: input signalC1: 1 µF capacitor, function: AC coupling and DC offset storageD1: 1N4148 small-signal diode, function: clamps the minimum voltage levelR1: 100 kΩ resistor, function: provides a discharge path and defines the load

Wiring guide

V1: connects between nodeVIN(positive) and node0(GND).C1: connects between nodeVINand nodeVOUT.D1: connects between node0(anode) and nodeVOUT(cathode).R1: connects between nodeVOUTand node0(GND).

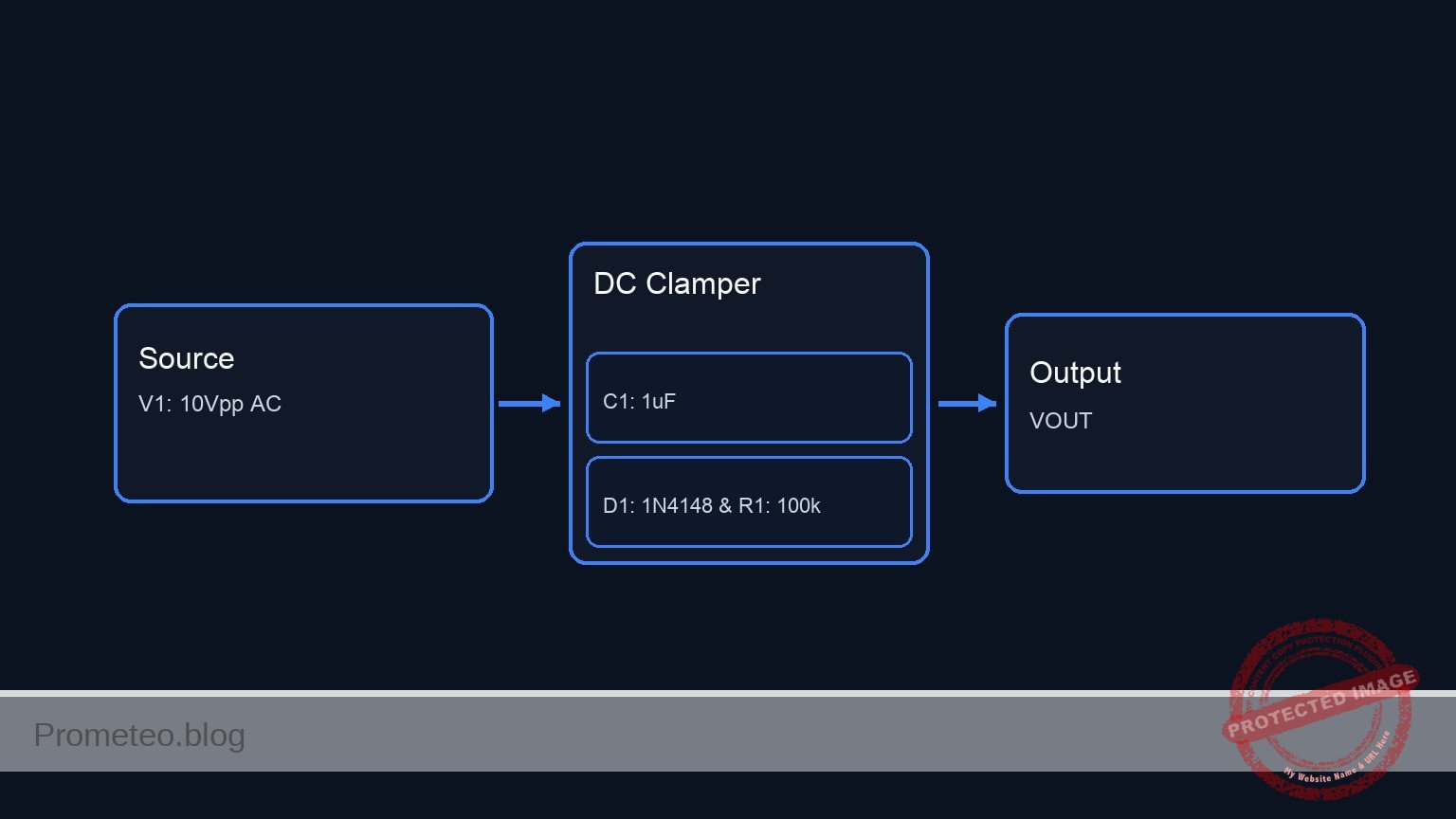

Conceptual block diagram

Schematic

[ V1: 10Vpp AC ] --(VIN)--> [ C1: 1µF ] --(VOUT)--+--> [ R1: 100 kΩ ] --> GND

|

+--> [ D1: 1N4148 Cathode ] --(Anode)--> GND

Measurements and tests

- Signal Generation: Connect your function generator or AC source to provide a 10 Vpp sine wave at 1 kHz to node

VIN. - Input Verification: Probe node

VINwith an oscilloscope channel (DC coupled). Verify theV_in_waveformswings symmetrically from -5 V to +5 V. - Output Waveform: Probe node

VOUTwith a second oscilloscope channel (DC coupled). Observe theV_out_waveform. It should swing approximately from -0.7 V to +9.3 V. - DC Offset Measurement: Switch your digital multimeter (DMM) to DC Voltage mode and measure node

VOUTrelative to node0. You should read a positiveDC_offsetof approximately +4.3 V. - Time Constant Check: Note how the output waveform maintains its shape. The high value of

R1ensures the capacitor does not discharge significantly between cycles.

SPICE netlist and simulation

Reference SPICE Netlist (ngspice)

* Practical case: DC level clamper circuit

.width out=256

* Input Signal: 5V peak (10Vpp), 1kHz sine wave

V1 VIN 0 SINE(0 5 1k)

* AC coupling and DC offset storage capacitor

C1 VIN VOUT 1u

* Clamping diode (Anode to GND, Cathode to VOUT)

D1 0 VOUT 1N4148

* Load resistor and discharge path

R1 VOUT 0 100k

* Standard 1N4148 diode model

.model 1N4148 D(IS=4.35E-9 N=1.906 BV=110 IBV=0.0001 RS=0.6458 CJO=1.20E-11 M=0.3333 VJ=0.75 TT=3.48E-9)

* Transient analysis for 5 milliseconds to capture 5 full cycles of the 1kHz signal

.tran 10u 5m

* Output directives (Input and Output nodes first)

.print tran V(VIN) V(VOUT)

.op

.endCopy this content into a .cir file and run with ngspice.

Simulation Results (Transient Analysis)

Show raw data table (509 rows)

Index time v(vin) v(vout) 0 0.000000e+00 0.000000e+00 -2.62072e-15 1 1.000000e-07 3.141592e-03 3.141552e-03 2 1.768596e-07 5.556208e-03 5.556134e-03 3 3.305789e-07 1.038543e-02 1.038529e-02 4 6.380174e-07 2.004385e-02 2.004355e-02 5 1.252894e-06 3.936043e-02 3.935972e-02 6 2.482649e-06 7.799154e-02 7.798965e-02 7 4.942157e-06 1.552375e-01 1.552318e-01 8 9.861173e-06 3.095997e-01 3.095809e-01 9 1.969921e-05 6.172898e-01 6.172223e-01 10 2.969921e-05 9.276226e-01 9.274748e-01 11 3.969921e-05 1.234294e+00 1.234036e+00 12 4.969921e-05 1.536095e+00 1.535695e+00 13 5.969921e-05 1.831833e+00 1.831263e+00 14 6.969921e-05 2.120342e+00 2.119572e+00 15 7.969921e-05 2.400483e+00 2.399485e+00 16 8.969921e-05 2.671151e+00 2.669897e+00 17 9.969921e-05 2.931276e+00 2.929740e+00 18 1.096992e-04 3.179833e+00 3.177990e+00 19 1.196992e-04 3.415841e+00 3.413667e+00 20 1.296992e-04 3.638368e+00 3.635840e+00 21 1.396992e-04 3.846536e+00 3.843632e+00 22 1.496992e-04 4.039523e+00 4.036224e+00 23 1.596992e-04 4.216569e+00 4.212856e+00 ... (485 more rows) ...

Common mistakes and how to avoid them

- Reversing the diode polarity: Placing the diode with the cathode to GND will create a negative clamper instead of a positive one. Always double-check the black band (cathode) orientation on the physical diode.

- Using too small of a load resistor (R1): If

R1is too small, the RC time constant will be shorter than the signal’s period, causing the capacitor to discharge too quickly and distorting the output waveform into a «shark fin» shape. - Using a polarized capacitor incorrectly: If you use an electrolytic capacitor for

C1, the positive leg must face the side with the higher average DC voltage (in this positive clamper case, facing nodeVOUT).

Troubleshooting

- Symptom: The output waveform is identical to the input waveform (centered at 0 V).

- Cause: The diode

D1is open, disconnected, or the capacitorC1is shorted. - Fix: Check diode continuity with a multimeter and ensure the capacitor is wired in series with the signal.

- Cause: The diode

- Symptom: The output waveform is flat at 0 V or -0.7 V.

- Cause: The diode

D1is shorted to ground, orVOUTis accidentally tied directly to GND. - Fix: Inspect the breadboard wiring at node

VOUTand replace the diode if it fails a diode-mode test.

- Cause: The diode

- Symptom: The DC level is correct, but the waveform has severe droop or tilt on the flat edges.

- Cause: The RC time constant is too low for the 1 kHz frequency.

- Fix: Increase the value of

R1(e.g., from 10 kΩ to 100 kΩ) or increaseC1to prevent premature discharge.

Possible improvements and extensions

- Biased Clamper: Add a small DC voltage source (e.g., a 1.5 V battery) in series with the diode

D1(between the anode and GND) to clamp the signal to an arbitrary reference level other than -0.7 V. - Negative Clamper Conversion: Reverse the direction of

D1(anode toVOUT, cathode to0) and observe how the entire AC waveform is shifted downward, sitting entirely below +0.7 V.

More Practical Cases on Prometeo.blog

Find this product and/or books on this topic on Amazon

As an Amazon Associate, I earn from qualifying purchases. If you buy through this link, you help keep this project running.