Nivel: Medio – Construye un circuito de memoria estable para eliminar el ruido de interruptores mecánicos usando compuertas NAND acopladas en cruz.

Objetivo y caso de uso

En este caso práctico, construirás un Latch Set-Reset (SR) utilizando un CI 74HC00. Al disponer dos compuertas NAND en una topología de retroalimentación acoplada en cruz, el circuito crea un elemento de memoria biestable que ignora el ruido mecánico de «rebote» generado cuando se cierran los contactos de un interruptor físico.

Por qué es útil:

* Interfaz con interruptores mecánicos: Esencial para leer botones en sistemas digitales sin disparos falsos.

* Interrupciones de microcontrolador: Proporciona un flanco limpio (subida/bajada) para disparar interrupciones de hardware de manera confiable.

* Retención de estado: Mantiene el último estado conocido (Set o Reset) incluso después de que se libera el disparador de entrada (retorno a reposo).

* Control industrial: Utilizado en circuitos de control de motores «Marcha/Parada» donde la estabilidad es crítica para la seguridad.

Resultado esperado:

* Salida Q: Permanece en ALTO (5 V) cuando se dispara Set y se mantiene en ALTO hasta que se dispara Reset.

* Salida Q_bar: Siempre la inversa de Q (Lógica BAJA cuando Q es ALTA).

* Retroalimentación visual: Dos LEDs (Verde y Rojo) indicando claramente el estado almacenado.

* Inmunidad al ruido: La salida transiciona una vez limpiamente, incluso si los contactos del interruptor rebotan múltiples veces en milisegundos.

Público objetivo y nivel: Estudiantes de electrónica y aficionados de nivel intermedio.

Materiales

- V1: Fuente de alimentación de 5 V DC

- U1: 74HC00 (Cuádruple compuerta NAND de 2 entradas)

- SW1: Interruptor SPDT (Un Polo Doble Tiro), función: selector Set/Reset

- R1: Resistencia de 10 kΩ, función: pull-up para SET_N

- R2: Resistencia de 10 kΩ, función: pull-up para RESET_N

- R3: Resistencia de 330 Ω, función: limitación de corriente LED para Q

- R4: Resistencia de 330 Ω, función: limitación de corriente LED para Q_bar

- D1: LED Verde, función: Indicador para Estado Q (Activo)

- D2: LED Rojo, función: Indicador para Estado Q_bar (Inactivo)

- C1: Condensador de 100 nF, función: desacople para pines de alimentación de U1

Pin-out del CI utilizado

Chip: 74HC00 (Cuádruple compuerta NAND de 2 entradas)

| Pin | Nombre | Función lógica | Conexión en este caso |

|---|---|---|---|

| 1 | 1 A | Entrada | Conecta al Nodo SET_N |

| 2 | 1B | Entrada | Conecta al Nodo Q_BAR (Retroalimentación) |

| 3 | 1Y | Salida | Conecta al Nodo Q |

| 4 | 2 A | Entrada | Conecta al Nodo RESET_N |

| 5 | 2B | Entrada | Conecta al Nodo Q (Retroalimentación) |

| 6 | 2Y | Salida | Conecta al Nodo Q_BAR |

| 7 | GND | Tierra | Conecta al Nodo 0 |

| 14 | VCC | Alimentación | Conecta al Nodo VCC (5 V) |

Guía de conexionado

- Fuente de Alimentación:

- Conecta el terminal positivo de

V1al nodoVCC. - Conecta el terminal negativo de

V1al nodo0(GND). - Conecta

C1entreVCCy0(cerca de U1). - Conecta el pin 14 de

U1aVCC. -

Conecta el pin 7 de

U1a0. -

Etapa de Entrada (Interruptor y Pull-ups):

- Conecta

R1entreVCCy el nodoSET_N. - Conecta

R2entreVCCy el nodoRESET_N. - Conecta el terminal Común de

SW1al nodo0. - Conecta el terminal Normalmente Abierto (NO) de

SW1al nodoSET_N. -

Conecta el terminal Normalmente Cerrado (NC) de

SW1al nodoRESET_N. (Nota: Alternar SW1 lleva una línea a Bajo mientras la otra permanece en Alto). -

Núcleo Lógico (NANDs acopladas en cruz):

- Conecta el pin 1 (1 A) de

U1al nodoSET_N. - Conecta el pin 2 (1B) de

U1al nodoQ_BAR. - Conecta el pin 3 (1Y) de

U1al nodoQ. - Conecta el pin 4 (2 A) de

U1al nodoRESET_N. - Conecta el pin 5 (2B) de

U1al nodoQ. -

Conecta el pin 6 (2Y) de

U1al nodoQ_BAR. -

Etapa de Salida (Indicadores):

- Conecta

R3entre el nodoQy el Ánodo deD1. - Conecta el Cátodo de

D1al nodo0. - Conecta

R4entre el nodoQ_BARy el Ánodo deD2. - Conecta el Cátodo de

D2al nodo0.

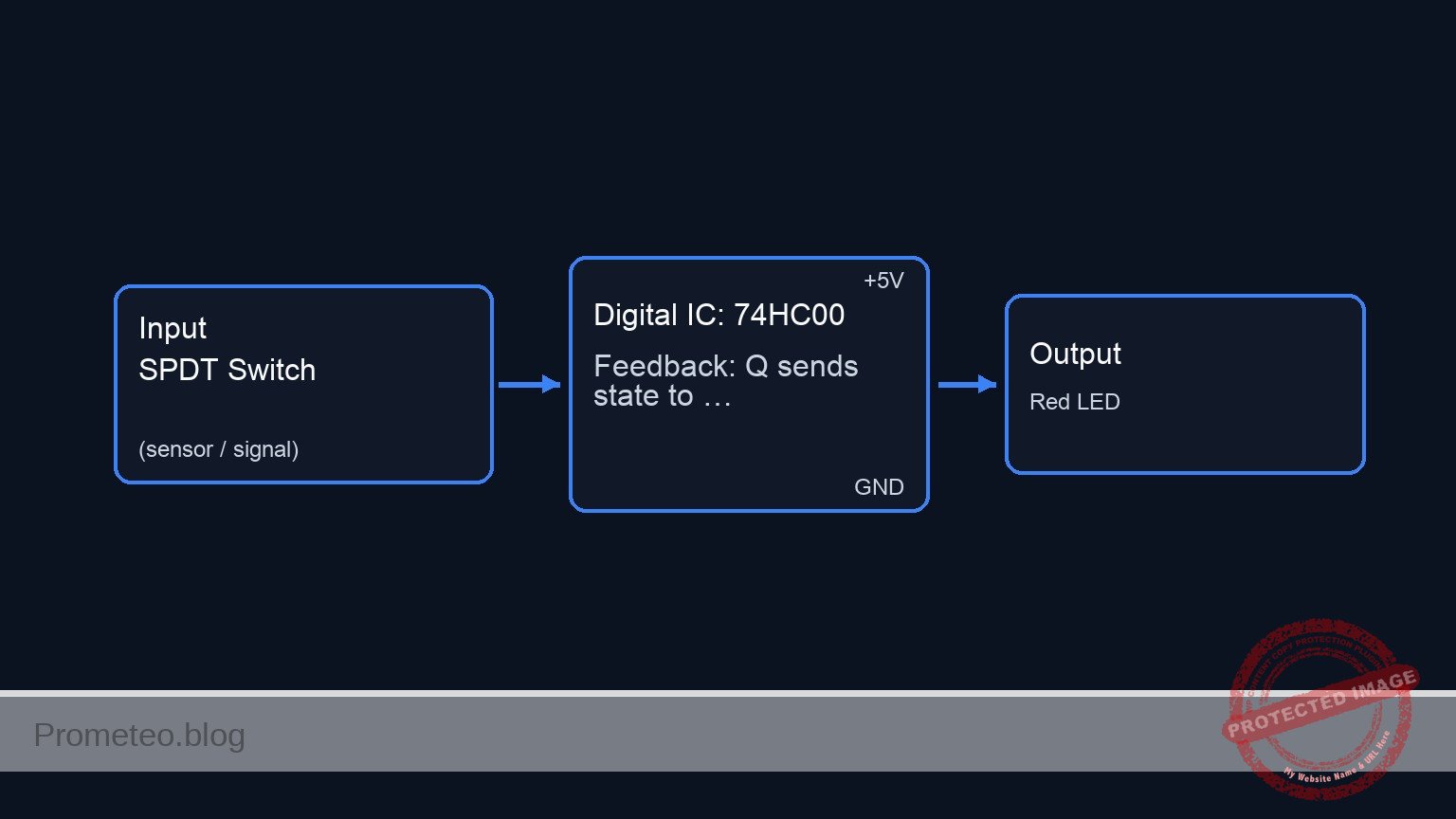

Diagrama de bloques conceptual

Esquemático

Title: Practical case: Debouncing SR Latch with NAND

INPUT STAGE (Switch & Pull-ups) LOGIC CORE (74HC00 Latch) OUTPUT STAGE (Indicators)

================================ ========================= =========================

[ VCC ]

|

V

[ R1: 10k Pull-up ]

|

V

(Node: SET_N) --------------------------> [ U1: NAND Gate A ] --(Signal: Q)-----> [ R3: 330 ] --> [ D1: Green LED ] --> GND

^ ^ |

| | |

[ SW1: SPDT Switch ] | +--(Feedback: Q sends state to Gate B)

(Connects GND to SET_N or RESET_N) |

| +--(Feedback: Q_BAR maintains state of Gate A)

v |

(Node: RESET_N) ------------------------> [ U1: NAND Gate B ] --(Signal: Q_BAR)-> [ R4: 330 ] --> [ D2: Red LED ] ----> GND

^

|

[ R2: 10k Pull-up ]

|

^

|

[ VCC ]

POWER & DECOUPLING:

[ VCC ] --(Power)--> [ U1: Pin 14 ]

[ GND ] --(Ground)--> [ U1: Pin 7 ]

[ VCC ] --(Filter)--> [ C1: 100nF ] --> [ GND ]

Tabla de verdad

Las entradas del Latch SR NAND son Activas en Bajo.

| SET_N (Entrada) | RESET_N (Entrada) | Q (Salida) | Q_bar (Salida) | Descripción del estado |

|---|---|---|---|---|

| 1 (Alto) | 1 (Alto) | Q Anterior | Q_bar Anterior | Retención (Memoria) |

| 0 (Bajo) | 1 (Alto) | 1 | 0 | Set |

| 1 (Alto) | 0 (Bajo) | 0 | 1 | Reset |

| 0 (Bajo) | 0 (Bajo) | 1 | 1 | Inválido (Evitar) |

Mediciones y pruebas

- Encendido inicial: Enciende la fuente de 5 V. Asegúrate de que

SW1esté en una posición específica. - Verificar Reset: Alterna

SW1para llevarRESET_Na Bajo (ySET_Na Alto).- Confirma que el LED Rojo (

D2, Q_bar) se ENCIENDE. - Confirma que el LED Verde (

D1, Q) se APAGA. - Mide el voltaje en

Q: debería ser aprox 0 V.

- Confirma que el LED Rojo (

- Verificar Set: Alterna

SW1para llevarSET_Na Bajo.- Confirma que el LED Verde (

D1, Q) se ENCIENDE. - Confirma que el LED Rojo (

D2, Q_bar) se APAGA. - Mide el voltaje en

Q: debería ser aprox 5 V.

- Confirma que el LED Verde (

- Prueba de antirrebote: Mientras mueves el interruptor, observa los LEDs. Deberían cambiar de estado instantáneamente sin parpadear, incluso si el contacto del interruptor es imperfecto.

- Prueba de desconexión (Estado de retención): Si desconectas los cables del interruptor para que ambas entradas sean llevadas a Alto por R1/R2, los LEDs deben mantener su último estado válido.

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice)

* Title: Practical case: Debouncing SR Latch with NAND

* NGSPICE Netlist

.width out=256

* --- Power Supply ---

V1 VCC 0 DC 5

C1 VCC 0 100n

* --- Input Stage (Switch and Pull-ups) ---

* R1 Pull-up for SET_N

R1 VCC SET_N 10k

* R2 Pull-up for RESET_N

R2 VCC RESET_N 10k

* --- Switch Simulation (SW1 SPDT) ---

* Control Signal Source

V_SW_CTRL CTRL 0 PULSE(0 5 100u 1u 1u 200u 600u)

* Inverted control signal for the NC contact

B_SW_INV CTRL_N 0 V=5-V(CTRL)

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

Resultados de Simulación (Transitorio)

Show raw data table (1072 rows)

Index time v(set_n) v(q) v(reset_n) v(q_bar) v(ctrl) 0 0.000000e+00 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 1 1.000000e-08 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 2 2.000000e-08 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 3 4.000000e-08 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 4 8.000000e-08 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 5 1.600000e-07 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 6 3.200000e-07 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 7 6.400000e-07 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 8 1.280000e-06 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 9 2.280000e-06 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 10 3.280000e-06 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 11 4.280000e-06 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 12 5.280000e-06 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 13 6.280000e-06 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 14 7.280000e-06 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 15 8.280000e-06 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 16 9.280000e-06 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 17 1.028000e-05 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 18 1.128000e-05 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 19 1.228000e-05 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 20 1.328000e-05 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 21 1.428000e-05 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 22 1.528000e-05 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 23 1.628000e-05 4.999500e+00 3.709206e-68 4.999950e-05 5.000000e+00 0.000000e+00 ... (1048 more rows) ...

Errores comunes y cómo evitarlos

- Dejar entradas flotando: Si quitas el interruptor y no tienes las resistencias R1/R2, las entradas flotan, causando oscilación impredecible. Solución: Usa siempre resistencias pull-up (10 kΩ) en las entradas del latch NAND.

- Confundir Activo en Bajo vs. Activo en Alto: Los usuarios a menudo esperan que un «1» active el latch. Un latch NAND se activa cuando la entrada va a «0». Solución: Recuerda que los latches NAND se disparan con pulsos a tierra (Bajo).

- Estado prohibido: presionar dos botones simultáneamente (si se usan botones en lugar de SPDT) crea un 0 Lógico en ambas entradas, forzando ambas salidas a Alto. Solución: Evita mecánicamente las pulsaciones simultáneas o diseña lógica para priorizar una entrada.

Solución de problemas

- Ambos LEDs están ENCENDIDOS:

- Causa: Tanto

SET_NcomoRESET_Nestán conectados a Tierra (Lógica 0) simultáneamente. - Solución: Revisa el cableado del interruptor; asegúrate de no estar cortocircuitando ambas entradas a tierra.

- Causa: Tanto

- El circuito no retiene el estado (los LEDs parpadean o siguen al interruptor vagamente):

- Causa: Falta la conexión de retroalimentación.

- Solución: Asegúrate de que el cable del Pin 3 (

Q) vaya al Pin 5, y el del Pin 6 (Q_BAR) vaya al Pin 2.

- El chip se calienta:

- Causa: Cortocircuito en la salida o polaridad de alimentación invertida.

- Solución: Comprueba que R3 y R4 estén presentes (no conectes LEDs directamente a las salidas) y verifica que el Pin 14 sea 5 V y el Pin 7 sea GND.

Posibles mejoras y extensiones

- Latch SR con habilitación (Gated): Agrega dos compuertas NAND extra (usando las dos restantes en el 74HC00) para añadir una señal de «Enable» (Habilitación), convirtiéndolo en una celda de memoria síncrona.

- Controlador de contador digital: Usa la salida

Qpara manejar la entrada de reloj de un contador CD4017 o 74HC4017, demostrando que la pulsación manual del botón genera exactamente un pulso de reloj limpio.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.