Nivel: Medio — Calcular y verificar un resistor de base para conmutar de forma segura un transistor NPN desde una salida lógica.

Objetivo y caso de uso

Construirás un interruptor simple con transistor donde una salida lógica de 5 V controla un transistor NPN a través de un resistor de base. El objetivo es elegir el resistor para que el transistor encienda la carga de forma fiable sin exceder la corriente permitida de la salida lógica.

Por qué es útil:

– Para accionar un módulo de relé, zumbador o lámpara pequeña desde un pin de microcontrolador.

– Para controlar cargas que requieren más corriente de la que una salida lógica puede suministrar directamente.

– Para proteger una salida lógica de una corriente de base excesiva.

– Para aprender a verificar la saturación del transistor con mediciones reales de voltaje y corriente.

Resultado esperado:

– Cuando la salida lógica está en LOW, el transistor permanece en OFF y la carga queda desenergizada.

– Cuando la salida lógica está en HIGH, el transistor pasa a ON y la corriente de carga es de aproximadamente 20 mA.

– La corriente de base se mantiene por debajo del límite de la salida lógica, con un objetivo de aproximadamente 4.3 mA.

– El voltaje base-emisor medido es de aproximadamente 0.7 V cuando está en ON.

– El voltaje colector-emisor medido es bajo en saturación, típicamente por debajo de 0.2 V.

Público objetivo y nivel: Estudiantes con conocimientos básicos de circuitos de CC y transistores.

Materiales

V1: fuente de CC de 5 VVSIG: fuente lógica de 0 V / 5 V, función: señal de control para la base del transistorR1: resistor de 1 kΩ, función: limitación de corriente de baseR2: resistor de 150 Ω, función: limitación de corriente de carga para la rama del LEDD1: LED rojo, función: indicador visible de carga en el colectorQ1: transistor NPN 2N2222, función: interruptor low-sideM1: multímetro digital, función: mediciones de voltaje y corrienteM2: segundo multímetro opcional, función: comprobación simultánea de corriente

Guía de conexionado

Usa estos nombres de nodo: VCC, 0, VIN, VB, VC.

V1se conecta entreVCCy0.VSIGse conecta entreVINy0.R1se conecta entreVINyVB.- El colector de

Q1se conecta aVC. - La base de

Q1se conecta aVB. - El emisor de

Q1se conecta a0. R2se conecta entreVCCy el nodo del ánodo deD1.- El ánodo de

D1se conecta aR2; el cátodo deD1se conecta aVC.

Valores prácticos de diseño:

– Objetivo de corriente de carga: aproximadamente Ic = (5 V - 2.0 V - 0.2 V) / 150 Ω ≈ 18.7 mA

– Ganancia forzada para saturación: usar β_forced ≈ 10

– Corriente de base requerida: Ib ≈ Ic / 10 ≈ 1.9 mA

– Estimación del resistor de base: R1 ≈ (5 V - 0.7 V) / 1.9 mA ≈ 2.26 kΩ

Para hacer la conmutación más robusta, elige un valor estándar más bajo:

– R1 seleccionado = 1 kΩ

– Corriente de base esperada: Ib ≈ (5 V - 0.7 V) / 1 kΩ ≈ 4.3 mA

Este valor solo es adecuado si la salida lógica puede suministrar con seguridad al menos 4.3 mA.

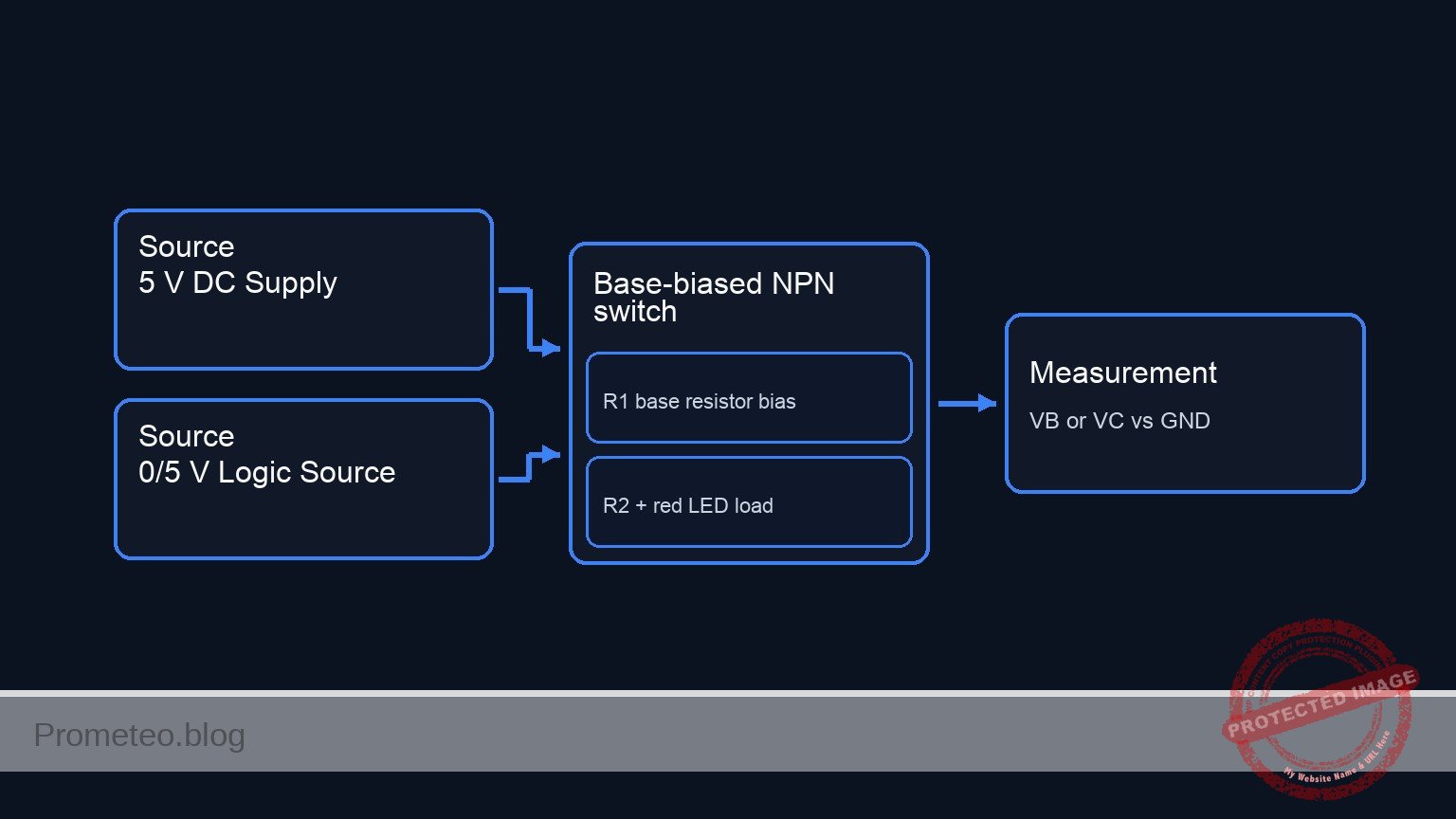

Diagrama de bloques conceptual

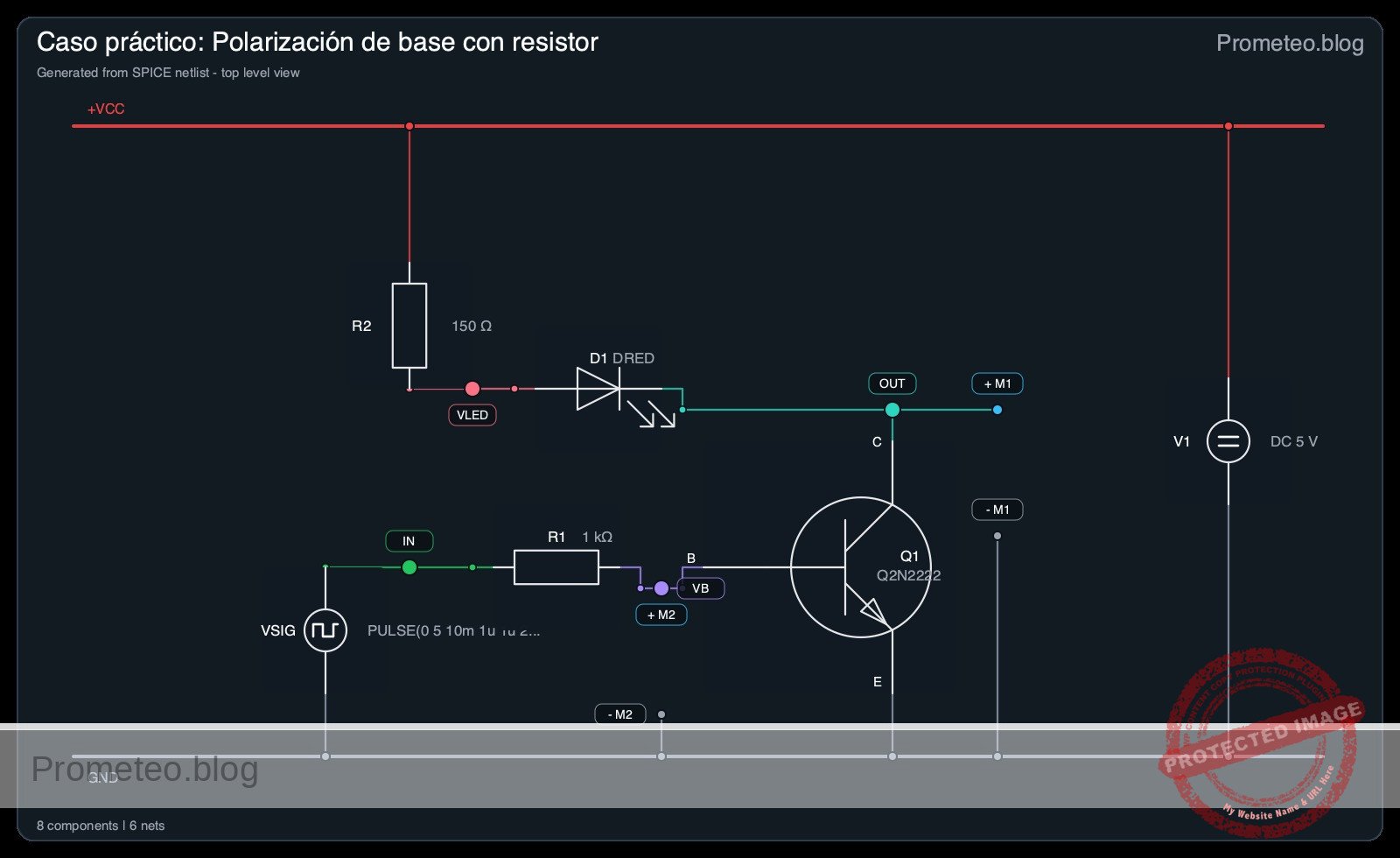

Esquemático

Practical case: Base Biasing with Resistor Power / load path: [ V1: 5 V DC Supply ] --(VCC)--> [ R2: 150 ohm ] --(LED current limit)--> [ D1: Red LED ] --(cathode at VC)--> [ Q1:C 2N2222 ] [ Q1:C 2N2222 ] --(collector-emitter path)--> [ Q1:E 2N2222 ] --(0 / GND)--> [ V1: 0 V ] Control / base path: [ VSIG: 0/5 V Logic Source ] --(VIN)--> [ R1: 1 kohm ] --(VB)--> [ Q1:B 2N2222 ] [ Q1:B 2N2222 ] --(base-emitter junction)--> [ Q1:E 2N2222 ] --(0 / GND)--> [ VSIG: 0 V ] Node labels: [ VIN ] --> [ R1 ] --> [ VB ] --> [ Q1:B ] [ VCC ] --> [ R2 ] --> [ D1 Anode ] [ D1 Cathode ] --> [ VC ] --> [ Q1:C ] [ Q1:E ] --> [ 0 / GND ] Optional measurements: [ M1 DMM ] --(measure V_B or V_C vs 0)--> [ VB / VC ] --> [ 0 / GND ] [ M2 DMM ] --(current mode, inserted in series where needed)--> [ Base path or Load path ]

Diagrama eléctrico

Mediciones y pruebas

- Comprobación con alimentación apagada

- Verifica todas las conexiones antes de aplicar alimentación.

- Confirma que el emisor de

Q1va a0. Confirma que

R1está en serie entreVINyVB.Prueba en estado OFF

- Ajusta

VSIG = 0 V. - Mide

VbdesdeVBhasta0: se espera cerca de0 V. - Mide

VcedesdeVChasta0: se espera cerca de5 V. - Observa

D1: debe estar en OFF. - Mide

Ib: se espera aproximadamente0 mA. Mide

Ic: se espera aproximadamente0 mA.Prueba en estado ON

- Ajusta

VSIG = 5 V. - Mide

Vb: se espera aproximadamente0.7 V. - Mide

Vbe: se espera aproximadamente entre0.65 Vy0.8 V. - Mide

Ibcolocando el medidor en serie conR1: se espera aproximadamente4.3 mA. - Mide

Vc: se espera bajo, típicamente por debajo de0.2 Va0.3 V. - Mide

Vce: se espera por debajo de0.2 Vsi se alcanza la saturación. - Mide

Icen serie con la trayectoria del colector: se espera aproximadamente entre18 mAy20 mA. Observa

D1: debe estar claramente en ON.Comprobación de seguridad de la salida lógica

- Compara la

Ibmedida con la corriente máxima de salida permitida por la salida lógica. Si la especificación de la salida lógica es menor que la corriente de base medida, aumenta

R1.Cálculo de verificación

- Calcula la ganancia medida en modo de conmutación:

Ic / Ib. - Ejemplo con valores medidos:

19 mA / 4.3 mA ≈ 4.4 Esto es consistente con conmutación en saturación, donde el transistor es sobreactivado intencionalmente.

Criterios de aprobación

Ibno excede el límite de la salida lógica.D1se enciende completamente con lógica HIGH y se apaga completamente con lógica LOW.Vceen estado ON es lo bastante bajo como para confirmar saturación.

Netlist SPICE y simulación

Netlist SPICE de referencia (ngspice) — extractoNetlist SPICE completo (ngspice)

* Practical case: Base Biasing with Resistor

.width out=256

V1 VCC 0 DC 5

VSIG VIN 0 PULSE(0 5 10m 1u 1u 245m 1s)

R1 VIN VB 1k

R2 VCC VLED 150

D1 VLED VC DRED

Q1 VC VB 0 Q2N2222

* Optional multimeter loading approximations (high impedance voltmeters)

RM1 VC 0 10Meg

RM2 VB 0 10Meg

* Alias nodes for guaranteed logging

VALIASIN IN VIN 0

VALIASOUT OUT VC 0

.model DRED D(IS=1e-18 N=2.0 RS=10 CJO=20p VJ=0.75 M=0.5 TT=50n BV=5 IBV=10u)

* ... (truncated in public view) ...Copia este contenido en un archivo .cir y ejecútalo con ngspice.

* Practical case: Base Biasing with Resistor

.width out=256

V1 VCC 0 DC 5

VSIG VIN 0 PULSE(0 5 10m 1u 1u 245m 1s)

R1 VIN VB 1k

R2 VCC VLED 150

D1 VLED VC DRED

Q1 VC VB 0 Q2N2222

* Optional multimeter loading approximations (high impedance voltmeters)

RM1 VC 0 10Meg

RM2 VB 0 10Meg

* Alias nodes for guaranteed logging

VALIASIN IN VIN 0

VALIASOUT OUT VC 0

.model DRED D(IS=1e-18 N=2.0 RS=10 CJO=20p VJ=0.75 M=0.5 TT=50n BV=5 IBV=10u)

.model Q2N2222 NPN(IS=1e-14 BF=200 VAF=100 IKF=0.1 ISE=1e-13 NE=1.5 BR=5 NR=1.0 VAR=25 IKR=0.05

+ RC=0.5 RE=0.2 RB=10 CJE=25p VJE=0.75 MJE=0.33 TF=0.4n XTF=2 CJC=8p VJC=0.55 MJC=0.33 TR=50n)

.save V(IN) V(OUT) V(VIN) V(VC) V(VB) V(VLED) I(V1) I(VSIG)

.op

.print op V(IN) V(OUT) V(VIN) V(VC) V(VB) V(VLED) I(V1) I(VSIG)

.tran 0.1m 250m

.print tran V(IN) V(OUT) V(VIN) V(VC) V(VB) V(VLED) I(V1) I(VSIG)

.endResultados de Simulación (Transitorio)

Show raw data table (2528 rows)

Index time v(in) v(out) v(vin) v(vc) v(vb) v(vled) v1#branch vsig#branch 0 0.000000e+00 0.000000e+00 3.623103e+00 0.000000e+00 3.623103e+00 3.624741e-09 4.999946e+00 -3.62318e-07 3.624741e-12 1 1.000000e-06 0.000000e+00 3.623104e+00 0.000000e+00 3.623104e+00 6.699379e-09 4.999946e+00 -3.62321e-07 6.699379e-12 2 2.000000e-06 0.000000e+00 3.623105e+00 0.000000e+00 3.623105e+00 6.506970e-09 4.999946e+00 -3.62321e-07 6.506970e-12 3 4.000000e-06 0.000000e+00 3.623106e+00 0.000000e+00 3.623106e+00 5.984372e-09 4.999946e+00 -3.62320e-07 5.984372e-12 4 8.000000e-06 0.000000e+00 3.623108e+00 0.000000e+00 3.623108e+00 5.188535e-09 4.999946e+00 -3.62320e-07 5.188535e-12 5 1.600000e-05 0.000000e+00 3.623110e+00 0.000000e+00 3.623110e+00 4.293865e-09 4.999946e+00 -3.62319e-07 4.293865e-12 6 3.200000e-05 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.693772e-09 4.999946e+00 -3.62318e-07 3.693772e-12 7 6.400000e-05 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.610539e-09 4.999946e+00 -3.62318e-07 3.610539e-12 8 1.280000e-04 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.631021e-09 4.999946e+00 -3.62318e-07 3.631021e-12 9 2.280000e-04 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.621414e-09 4.999946e+00 -3.62318e-07 3.621414e-12 10 3.280000e-04 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.626121e-09 4.999946e+00 -3.62318e-07 3.626121e-12 11 4.280000e-04 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.624676e-09 4.999946e+00 -3.62318e-07 3.624676e-12 12 5.280000e-04 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.623957e-09 4.999946e+00 -3.62318e-07 3.623957e-12 13 6.280000e-04 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.626113e-09 4.999946e+00 -3.62318e-07 3.626113e-12 14 7.280000e-04 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.623011e-09 4.999946e+00 -3.62318e-07 3.623011e-12 15 8.280000e-04 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.626745e-09 4.999946e+00 -3.62318e-07 3.626745e-12 16 9.280000e-04 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.622584e-09 4.999946e+00 -3.62318e-07 3.622584e-12 17 1.028000e-03 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.627045e-09 4.999946e+00 -3.62318e-07 3.627045e-12 18 1.128000e-03 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.622367e-09 4.999946e+00 -3.62318e-07 3.622367e-12 19 1.228000e-03 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.627168e-09 4.999946e+00 -3.62318e-07 3.627168e-12 20 1.328000e-03 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.622305e-09 4.999946e+00 -3.62318e-07 3.622305e-12 21 1.428000e-03 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.627229e-09 4.999946e+00 -3.62318e-07 3.627229e-12 22 1.528000e-03 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.622257e-09 4.999946e+00 -3.62318e-07 3.622257e-12 23 1.628000e-03 0.000000e+00 3.623112e+00 0.000000e+00 3.623112e+00 3.627228e-09 4.999946e+00 -3.62318e-07 3.627228e-12 ... (2504 more rows) ...

Errores comunes y cómo evitarlos

- No usar resistor de base

- Error: conectar la salida lógica directamente a la base del transistor.

- Resultado: corriente de base excesiva y posible daño a la salida lógica.

Solución: coloca siempre

R1entreVINyVB.Elegir un resistor de base demasiado grande

- Error: usar

R1 = 10 kΩsin comprobar la corriente. - Resultado: la corriente de base puede ser demasiado baja, por lo que el transistor puede no saturarse.

Solución: calcula

Iba partir de la corriente de carga y usa una ganancia forzada de aproximadamente 10 para conmutación.Invertir los terminales del transistor

- Error: intercambiar colector y emisor.

- Resultado: voltajes anómalos, corriente de carga débil o ausencia de conmutación.

- Solución: confirma el pinout del 2N2222 en su hoja de datos antes de cablear.

Solución de problemas

- Síntoma: el LED nunca se enciende

- Causa:

VSIGno está llegando a 5 V, o la base deQ1no está conectada a través deR1. Solución: mide

VINyVB; verifica la continuidad deR1y el pinout del transistor.Síntoma: el LED está tenue

- Causa: el transistor no está saturado porque

R1es demasiado grande. Solución: reduce

R1después de comprobar el límite de corriente de la salida lógica.Síntoma: el voltaje de salida lógica cae cuando está en ON

- Causa: la demanda de corriente de base es demasiado alta para la fuente lógica.

Solución: aumenta

R1o usa una etapa driver con transistor.Síntoma: el LED permanece encendido todo el tiempo

- Causa: conexionado incorrecto en el nodo del colector o polarización de base no intencionada.

Solución: comprueba que el emisor de

Q1está en0y queVINrealmente baja a 0 V en el estado LOW.Síntoma: la

Vcemedida es alta cuando está en ON- Causa: corriente de base insuficiente o cableado incorrecto de la carga del colector.

- Solución: verifica

Ib, recalculaR1y compruebaR2y la orientación deD1.

Posibles mejoras y extensiones

- Añade un resistor pull-down de

10 kΩdesdeVBhasta0para que el transistor permanezca en OFF si la fuente lógica se desconecta o queda en alta impedancia. - Sustituye la carga LED por una bobina de relé y añade un diodo flyback en paralelo con la bobina para estudiar la conmutación de transistores con cargas inductivas.

Más Casos Prácticos en Prometeo.blog

Encuentra este producto y/o libros sobre este tema en Amazon

Como afiliado de Amazon, gano con las compras que cumplan los requisitos. Si compras a través de este enlace, ayudas a mantener este proyecto.